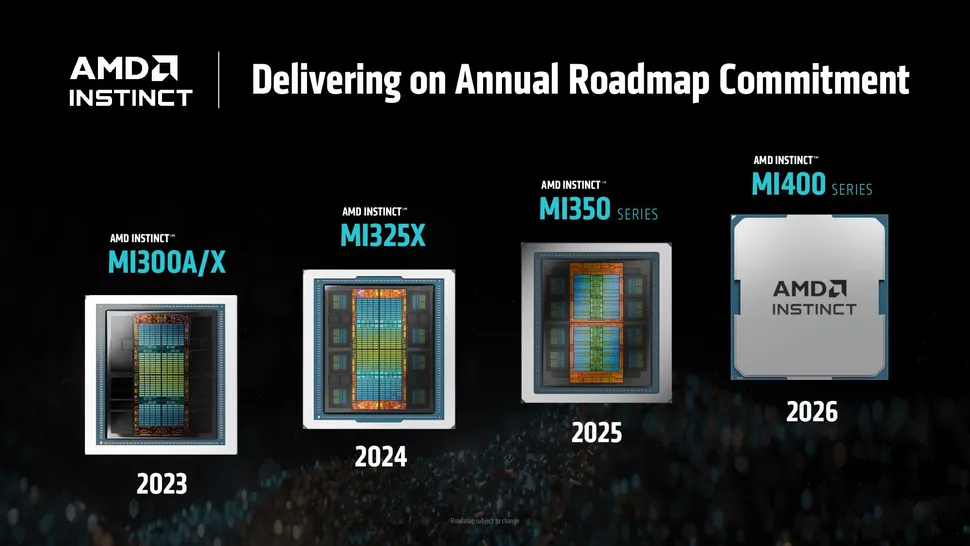

تم إصدار وحدة معالجة الرسوميات AI من سلسلة Instinct MI350X من AMD، مع بنية CDNA 4 المتطورة، في شهر يونيو، ولكن ندوة ISSCC الأخيرة في سان فرانسيسكو هي المكان الذي حصلنا فيه على أول غوص عميق في الهندسة الكامنة وراءها.

أثناء صعوده إلى المسرح في 16 فبراير، تحدث راماسامي أديكالافان، مهندس التصميم زميل AMD، عن كيفية تمكن AMD من ملاءمة ما يقرب من ضعف إنتاجية الحوسبة في نفس منطقة القالب مثل سابقتها، ولماذا يحتوي MI355X على وحدات حسابية أقل من وحدة معالجة الرسومات التي تحل محلها.

وحدات حسابية أقل، إنتاجية أكبر

يحتوي كل قالب Accelerator Complex Die (XCD) في MI355X على 32 وحدة حسابية نشطة، انخفاضًا من 38 في MI300X، لكن AMD ضاعفت إنتاجية كل CU FP8 في هذه العملية – من 4,096 FLOPS لكل ساعة إلى 8,192 – عن طريق إعادة تصميم أجهزة تنفيذ المصفوفة بدلاً من مجرد إضافة المزيد منها.

تبنت الشركة أيضًا ما أسمته استراتيجية المشاركة الانتقائية، حيث بدلاً من بناء أجهزة مخصصة بالكامل لكل تنسيق رقمي (وهو أمر مكلف في منطقة القالب) أو مشاركة جميع الأجهزة عبر كل تنسيق (أرخص، ولكن غير فعال)، قامت AMD بتحليل كل مكون حسابي على حدة وشاركت فقط عندما تكون عقوبة الطاقة مقبولة. على هذا النحو، يوفر جهاز MI355X خمسة بيتافلوب من حوسبة FP8، وهو تحسن بمقدار 1.9 مرة مقارنة بـ MI300X، مع تركيب نفس مساحة القالب البالغة 110 مم² لكل قالب مجمع التسريع (XCD).

يقول أديكالافان: “إن عدد 32-CU هو اختيار مقصود”. “إنه يحافظ على بنية نظيفة تعتمد على قوة اثنين، مما يبسط تبليط الموتر وتقسيم عبء العمل لنواة الذكاء الاصطناعي.” يُسهّل عدد CU القوي على نواة الذكاء الاصطناعي تقسيم العمل بالتساوي عبر الأجهزة، مما يقلل من تأثير الذيل، وهو عقوبة الأداء التي تحدث عندما لا تملأ الدفعة الأخيرة من العمل موارد الحوسبة المتاحة.

اكتسب XCD أيضًا طبقتين توجيه معدنيتين إضافيتين من خلال القفز من N5 الخاص بـ TSMC إلى N3P، مما أدى إلى زيادة كومة المعدن من 15 إلى 17 طبقة ومعالجة مشكلة نهاية الخط الخلفية المتزايدة. وقال أديكالافان: “على الرغم من تباطؤ قانون مور، إلا أننا لا نزال نحصل على بعض القياس الخطي الجيد في الكثافة المنطقية”. “ومع ذلك، فإن كثافة التوجيه لا تتماشى.” عند 3 نانومتر، تمثل الأسلاك الآن جزءًا أكبر من إجمالي طاقة التحويل عما كانت عليه في الأجيال السابقة، لذلك استجابت AMD بتحسين مخطط الأرضية بعناية وخوارزميات تحديد الموضع المستندة إلى ML لتقليل طول السلك على شبكات الإشارة النشطة.

بالاشتراك مع خلايا بوابة الساعة المخصصة القائمة على النشاط، والتي تكتشف متى يؤدي تدفق البيانات من الأصفار أو الآحاد المتكررة إلى تبديل الساعة وإيقاف تشغيلها دون داعٍ وفقًا لذلك، استهدفت AMD تقليلًا أكبر من 30٪ في سعة التبديل المحايدة للعملية لكل عملية مقارنةً بأجهزة XCD الخاصة بـ MI300X.

إعادة تصميم قالب الإدخال/الإخراج

استخدم MI300X أربع قوالب إدخال/إخراج منفصلة، لكن AMD خفضت ذلك إلى قالبين أكبر في MI355X، وهما متصلان ببعضهما البعض بشكل مباشر. تقول AMD إن هذا الدمج يحقق مكاسب ذات مغزى في الكفاءة تتجاوز مجرد تقليل عدد القوالب.

لقد مكن عدد أقل من عمليات العبور من القالب إلى الموت AMD من إزالة الدوائر المطلوبة سابقًا للتعامل مع عمليات عبور المجال وترجمات البروتوكول. ذهبت المنطقة المحررة إلى توسيع خط أنابيب بيانات Infinity Fabric بحيث يمكن توفير عرض النطاق الترددي الأقصى لـ HBM بجهد وترددات تشغيل أقل. يترتب على ذلك مطالبة AMD بقراءة عرض النطاق الترددي الأفضل لقراءة HBM بمقدار 1.3x لكل واط مقارنة بـ MI300X؛ زاد رقم النطاق الترددي الأولي بمقدار 1.5 مرة (من 5.3 إلى 8.0 تيرابايت/ثانية)، لكن مكاسب الكفاءة جاءت من تشغيل النسيج في نقطة تشغيل أقل استهلاكًا للطاقة.

استهدفت AMD أيضًا طاقة توصيل أقل بنسبة 20% تقريبًا على IOD من خلال ما وصفته بهندسة الأسلاك المخصصة، حيث قام مهندسو AMD بضبط أطوال المقاطع، وتحسين أنماط التوجيه، واختيار قواعد التوجيه غير الافتراضية. ومع ذلك، تعترف AMD بأن هذه الأرقام هي تقديرات سابقة لـ sukucib ebgubeerubg.

وفي الوقت نفسه، فإن مشاركة البيانات المحلية (LDS) الأكبر والأسرع – وهي ذاكرة مسودة على الرقاقة داخل كل وحدة حوسبة – “تعمل على تحسين استخدام وحدة حوسبة المصفوفة الموسعة حديثًا مع إعادة استخدام البيانات على الرقاقة على نطاق واسع”، كما يوضح أديكالافان. تعد LDS أكبر بكثير في سلسلة MI335X مقارنة بسلسلة MI300X، حيث تصل إلى 160 كيلو بايت لكل وحدة مقابل 64 كيلو بايت، مع ضعف عرض النطاق الترددي.

أثناء عمليات مضاعفة وتراكم المصفوفة، يقوم LDS بتغذية البيانات مباشرة إلى وحدات حساب المصفوفة، ويقلل LDS الأكبر عدد المرات التي يجب أن تصل فيها وحدة معالجة الرسومات إلى طبقات الذاكرة الأبطأ لإعادة تحميل بيانات المعامل. أضافت AMD أيضًا مسار تحميل LDS مباشرًا من ذاكرة التخزين المؤقت للبيانات L1، مما يلغي استخدام السجل المتوسط، مما يقلل من زمن انتقال الذاكرة لهذه العمليات بشكل أكبر.

أرقام الأداء (والمحاذير)

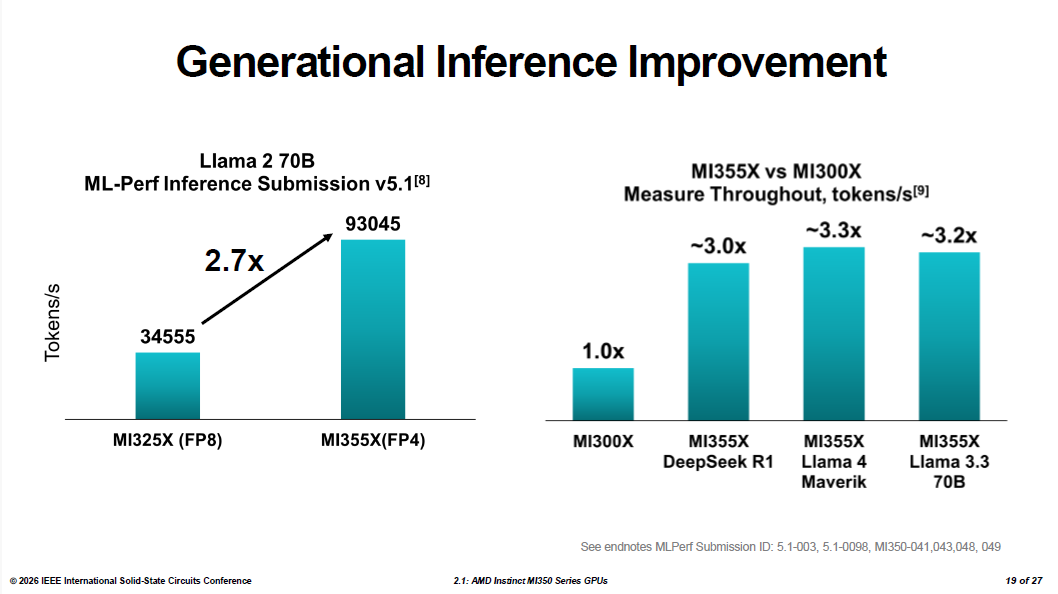

قدمت AMD MI355X إلى MLPerf Inference v5.1، حيث حققت 93,045 رمزًا في الثانية على معيار Llama 2 70B – وهو تحسن بمقدار 2.7x مقارنة بـ MI325X. في مقارنات الإنتاجية الداخلية، عند تشغيل استنتاج FP4 مقابل نتائج FP8 الخاصة بـ MI300X، أظهرت AMD تحسنًا تقريبًا بثلاثة أضعاف في إنشاء الرمز المميز عبر DeepSeek R1 وLlama 4 Maverick وLlama 3.3 70B.

ومن الجدير بالذكر أن هذه الأرقام تضع نتائج FP4 الخاصة بـ MI355X في مقابل FP8 الخاصة بـ MI300X، ولم يدعم MI300X FP4 أبدًا. لذلك، في حين أن هذه البيانات تظهر تحسنًا بين الأجيال في الممارسة العملية، إلا أنها لا تعزل الأجهزة عن تحسينات البرامج وتنسيق البيانات.

مقارنة التدريب مع Nvidia لها تحذير مماثل. تُظهر بيانات AMD أن جهاز MI355X يكمل عملية الضبط الدقيق لـ Llama 2 70B LoRA في 10.18 دقيقة، مقابل 11.15 دقيقة لـ GB200 – أسرع بحوالي 10%. جاءت نتيجة AMD من MLPerf Training v5.1 باستخدام FP4، في حين أن رقم Nvidia هو آخر نتيجة FP8 منشورة لـ GB200 من MLPerf Training v5.0؛ لم تقدم Nvidia نتيجة تدريب مماثلة على FP4.

وكان Adaikkalavan صريحًا بشأن ما تعكسه نتيجة التكافؤ: “نحن في الواقع نطابق أداء GB200 الأكثر تكلفة وتعقيدًا. ويخبرك هذا بعدة أشياء. أولاً، لدينا أجهزة قوية، وهو ما نعرفه دائمًا. وثانيًا، حققت أطر البرامج المفتوحة تقدمًا هائلاً.”

تُظهر حسابات AMD أن MI355X يحمل 288 جيجابايت من HBM3E مقابل 192 جيجابايت لـ B200، ويوفر ضعف إنتاجية FP64 تقريبًا – 2.1x مقارنة بـ B200. بالنسبة لأحمال عمل الاستدلال العام، يكون المسرّعان في حالة تكافؤ تقريبي. تجمع الذاكرة الأكبر حجمًا في MI355X ميزتها الأكثر اتساقًا في تشغيل النماذج الكبيرة دون توزيعها عبر وحدات معالجة الرسومات المتعددة.

يحتفظ كل من MI350X (1000 واط TBP، 2200 ميجا هرتز) والرائد MI355X (1400 واط TBP، 2400 ميجا هرتز) بنفس عامل الشكل المادي مثل MI300X. قامت AMD ببناء هذا القيد في المشروع منذ البداية، حيث صممت جيل CDNA 4 بأكمله ليعمل كترقية للبنية التحتية للخوادم القائمة على MI300 بدلاً من الحاجة إلى تصميمات حامل جديدة أو بنية تحتية للتبريد.

مع انتظار سلسلة MI400 في الأجنحة، ستلعب سلسلة MI350 قريبًا دورًا ثانويًا. تم تصميم MI400 بناءً على عملية TSMC's N2، مع 432 جيجابايت من HBM4 وضعف الحوسبة تقريبًا. تواصل AMD الوعد بهذه الرقائق للنصف الثاني من هذا العام. ولكن في عالم من المحتمل أن يكون فيه كل FLOP ذو قيمة AI، فمن المرجح أن تستمر AMD وعملائها في تحسين الأداء على عائلة MI350 لبعض الوقت في المستقبل.

التعليقات