على الرغم من أن أداء الذاكرة ذات النطاق الترددي العالي (HBM) قد زاد بمقدار أمر كبير منذ إنشائها قبل عقد من الزمن تقريبًا، إلا أن العديد من العناصر ظلت دون تغيير جوهري بين HBM1 وHBM3E. ولكن مع تطور الطلب على التطبيقات المتعطشة لعرض النطاق الترددي، يجب أن تتغير التكنولوجيا أيضًا لاستيعابها.

في المعلومات الجديدة التي تم الكشف عنها في منتدى OIP الأوروبي التابع لشركة TSMC في أواخر نوفمبر، ستقدم HBM4 وHBM4E أربعة تغييرات رئيسية. سيتلقى HBM4 واجهة 2048 بت وقوالب أساسية يتم إنتاجها باستخدام تقنيات المنطق المتقدمة. وفي الوقت نفسه، سيكون HBM4E قادرًا على استخدام قوالب القاعدة القابلة للتخصيص، والتي يمكن التحكم فيها من خلال واجهات مخصصة. هذه تحولات جذرية، وسيكون لها تأثير كبير في وقت أقرب مما تعتقد.

HBM4: الشيء الكبير التالي

HBM4 – الذي تم نشر مواصفاته رسميًا في وقت سابق من هذا العام – هو المعيار الذي يمهد الطريق لعدد من الابتكارات القادمة في سوق ذاكرة الذكاء الاصطناعي والحوسبة عالية الأداء.

تتميز كل حزمة ذاكرة HBM4 بواجهة 2,048 بت تدعم رسميًا معدلات نقل البيانات التي تصل إلى 8 جيجا بايت/ثانية، على الرغم من أن وحدات التحكم من متخصصي وحدات التحكم مثل Rambus وHBM4 المكدسات من كبار موردي DRAM تدعم بالفعل سرعات تصل إلى 10 جيجا بايت/ثانية أو أعلى، نظرًا لأن المنفذين يريدون الحصول على بعض الاحتياطي لمزيد من راحة البال.

يمكن لمجموعة مكدسة ذات واجهة 2048 بت تعمل بسرعة 12 جيجا بايت/ثانية أن توفر عرض نطاق ترددي يبلغ 2 تيرابايت/ثانية، وبالتالي فإن مسرع الذكاء الاصطناعي المزود بثمانية مجموعات HBM4 سيتمكن من الوصول إلى عرض نطاق ترددي محتمل يبلغ 16 تيرابايت/ثانية. ويمكن أن تكون 12 GT/s مجرد البداية. لاحظ أن Cadence تقدم بالفعل واجهة HBM4E المادية (PHY) مع دعم بسرعة 12.8 GT/s.

داخليًا، يعمل HBM4 على مضاعفة التزامن إلى 32 قناة مستقلة لكل حزمة (كل منها مقسمة إلى قناتين زائفتين)، مما يقلل من تعارضات البنوك ويزيد من كفاءة الإنتاجية في ظل أنماط وصول متوازية للغاية.

تدعم مجموعات HBM4 أيضًا أجهزة DRAM سعة 24 جيجا بايت و32 جيجا بايت وتوفر تكوينات لمجموعات 4-Hi و8-Hi و12-Hi و16-Hi، وبالتالي تمكين قدرات تصل إلى 64 جيجا بايت، مما يسمح ببناء مسرعات لنماذج الذكاء الاصطناعي من الجيل التالي بتريليونات من المعلمات. تتوقع Micron أن تصبح مكدسات سعة 64 جيجابايت شائعة مع HBM4E في وقت ما بعد أواخر عام 2027، وهو ما يتماشى مع خطط Nvidia لتزويد وحدة معالجة الرسومات Rubin Ultra بذاكرة HBM4E بسعة 1 تيرابايت.

تعمل المواصفات الكهربائية لـ HBM4 على توسيع جهود التشغيل مع خيارات VDDQ الخاصة بالبائع بين 0.679 فولت و0.963 فولت وVDDC من 0.97 فولت أو 1.07 فولت، مما يمكّن صانعي DRAM من ربط عروضهم لتحقيق الكفاءة أو التردد مع الحفاظ على التوافق مع المواصفات. على الجانب الأمني، يدعم HBM4 إدارة التحديث الموجه (DRFM) للتخفيف من هجمات المطرقة.

نظرًا لأن HBM4 يوسع واجهته إلى 2048 بت، فمن المفترض أن يحتوي على ضعف جهات اتصال الإدخال/الإخراج مقارنةً بمكدسات HBM من الجيل السابق. نظرًا لأنه كان من المستحيل تقريبًا إنتاج قالب أساسي مع التوجيه المناسب باستخدام تقنيات معالجة DRAM، تعاون صانعو الذاكرة مثل Micron وSamsung وSK hynix مع TSMC في وقت مبكر لضمان التوافق مع تقنيات التعبئة والتغليف CoWoS ولإنتاج قوالب قاعدة HBM4 باستخدام تقنيات التصنيع 12FFC أو N5.

في ذلك الوقت، كان يُعتقد أن 12FFC سيتم استخدامها لقوالب قاعدة HBM4 “العادية”، والتي سيتم دمجها مع معالجاتها المضيفة باستخدام تقنيات المعالجة 2.5D المتقدمة، في حين سيتم استخدام قوالب قاعدة N5 لذاكرة HBM4، والتي سيتم بعد ذلك دمجها باستخدام الارتباط المباشر على رقائق المنطق.

في منتدى OIP 2025 الأوروبي، لم تذكر TSMC أو شركاؤها قاعدة HBM4 المستندة إلى N5 للتكامل باستخدام الترابط الهجين أو التقنيات المماثلة، مما يعني على الأرجح أن المشروع ليس أولوية تمامًا في الوقت الحالي.

من المحتمل أن يؤدي دمج مجموعات ذاكرة HBM4 فوق معالج عالي الأداء إلى إنشاء كثافة حرارية كبيرة، مما قد يجعل من الصعب التبريد. من الممكن أيضًا أن تؤدي رقائق الحوسبة الساخنة إلى إتلاف أجهزة DRAM الساخنة، والعكس صحيح، ولكن هذه مجرد تكهنات.

قد تكون هناك أيضًا عمليات تكامل SoIC-X 3D مرتبطة هجينة، مع HBM4 المكدس فوق شرائح الحوسبة قيد التطوير، لكن مطوريها لا يريدون مشاركة النتائج حتى الآن.

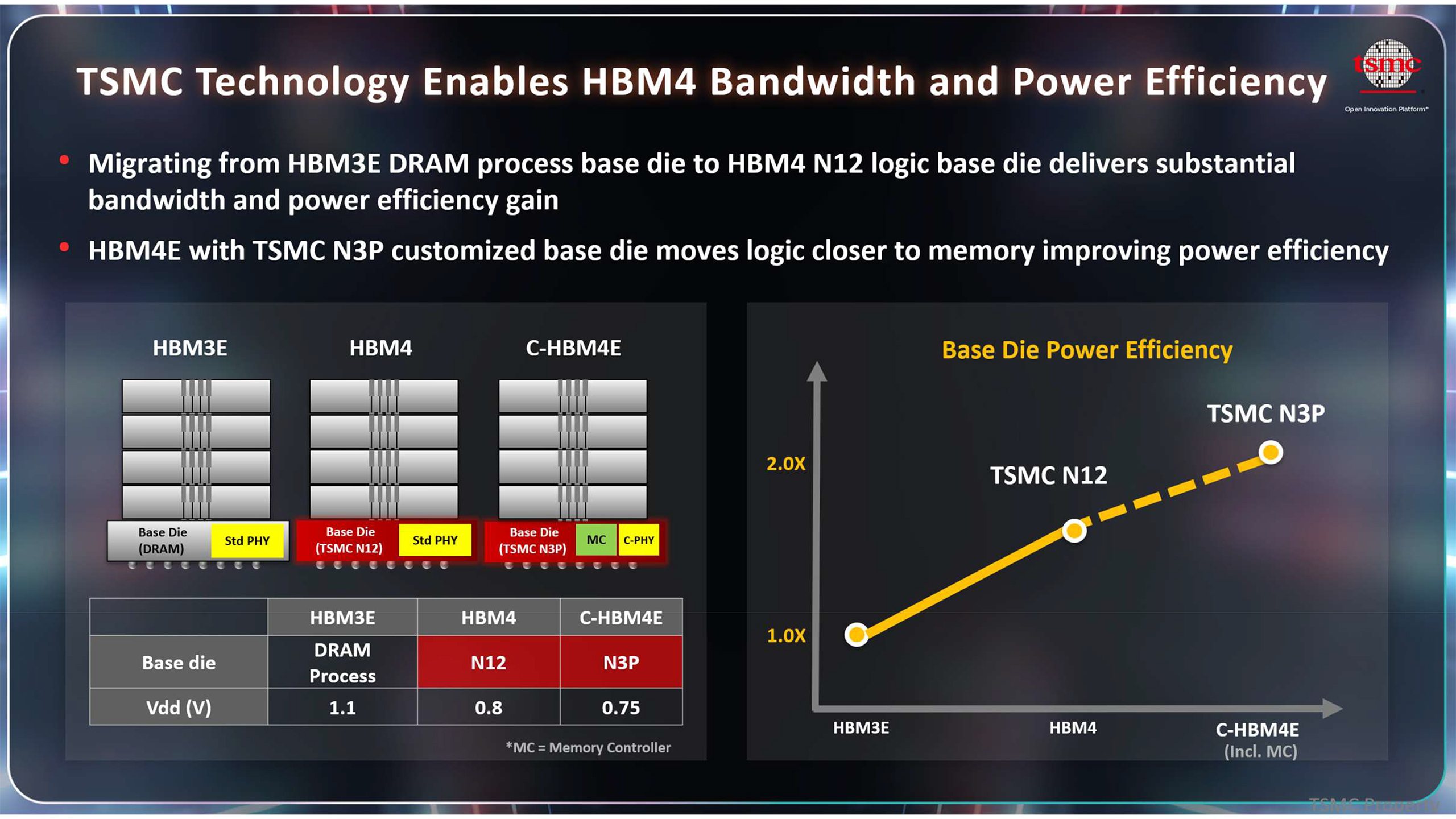

على أي حال، تستخدم قوالب قاعدة HBM4 التي تصنعها TSMC باستخدام تقنيات المعالجة 12FFC أو N5 منخفضة الطاقة، بالإضافة إلى قوالب قاعدة C-HBM4E المخصصة المنتجة على عقدة N3P الخاصة بشركة TSMC، جهدًا كهربائيًا أقل (0.8 فولت – 0.75 فولت مقابل 1.1 فولت في حالة HBM3E)، وهي أكثر كفاءة في استخدام الطاقة بما يصل إلى مرتين من القوالب الأساسية لذاكرة HBM3E المصنعة باستخدام تقنيات DRAM، وفقًا لشركة TSMC.

من ناحية أخرى، نظرًا لأن HBM4 يتطلب وحدة تحكم أكثر تطورًا وPHY أكبر وأكثر تعقيدًا مقارنةً بـ HBM3E (15 مم ^ 2 مقابل 11 مم ^ 2، وفقًا لـ GUC). ستكون أنظمة الذاكرة الفرعية لـ HBM4 أكثر جوعًا للطاقة من أنظمة HBM3E الفرعية أيضًا. ومع ذلك، ونظرًا لعرض النطاق الترددي الأعلى بشكل كبير، الذي تم تمكينه بواسطة HBM4، فستكون أكثر كفاءة في استخدام الطاقة والمساحة من سابقاتها.

أما بالنسبة لجاهزية IP، فقد قامت الجامعة الألمانية بالقاهرة بتسجيل HBM4 PHY IP الخاص بها على N3P في مارس 2025. وسيتم التحقق من صحة ذلك من خلال عينات ذاكرة HBM4 في الربع الأول من عام 2026، عندما تكون الشركة قادرة رسميًا على الادعاء بأن لديها حل ذاكرة HBM4 مثبتًا ومعتمدًا من السيليكون. بالإضافة إلى ذلك، سيكون IP متوافقًا مع جميع أنواع عبوات CoWoS (-S، -R، -L) ويمكنه معالجة مجموعة متنوعة من التطبيقات. تتوفر وحدات التحكم في الذاكرة HBM4 لدى مجموعة من الشركات، بما في ذلك Rambus. مطورو EDA مثل Cadence وSiemens EDA وSynopsys.

HBM4E: عرض نطاق ترددي أعلى بمقدار 2.5 مرة من HBM3E

مع طرح واجهة ذاكرة HBM4 ذات 2048 بت، كان على أعضاء JEDEC خفض معدلات نقل البيانات القصوى إلى 8 جيجا بايت/ثانية من حوالي 9.4 جيجا بايت/ثانية مدعومة بـ HBM3E، والتي لا تزال تتيح زيادة كبيرة في عرض النطاق الترددي. ومع ذلك، تم إعداد HBM4E لدفع الحدود الكهربائية والإشارات إلى أعلى من خلال دعم معدلات البيانات لكل طرف إلى 12 GT/s (من خلال تحسين PHY لتحسين هامش الإشارة والتحكم في الارتعاش عند الترددات الأعلى) وتوسيع نطاق النطاق الترددي الإجمالي إلى حوالي 3 تيرابايت/ثانية، مع الحفاظ على واجهة 2048 بت وهندسة 32 قناة. ونتيجة لذلك، فإن عرض النطاق الترددي الذي توفره مجموعات HBM4E سيكون أعلى بمقدار 2.5 مرة مقارنة بـ HBM3E، وحتى عندما يتم أخذ المساحة وطاقة PHY في الاعتبار، فإن HBM4E سيكون أكثر كفاءة في استخدام الطاقة بمقدار 1.7 مرة وكفاءة في المساحة بمقدار 1.8 مرة، وفقًا لـ GUC.

| الصف 0 – الخلية 0 |

HBM3E |

HBM4E |

اختلاف |

|

توافر العملية |

7 نانومتر، 5/4 نانومتر، 3 نانومتر |

3 نانومتر، 2 نانومتر |

الصف 1 – الخلية 3 |

|

عرض الإدخال/الإخراج، القنوات |

1024 بت، 16 قناة |

2048 بت، 32 قناة |

2x |

|

السرعة لكل دبوس |

9.4 جيجابت في الثانية |

12 جيجابت في الثانية |

1.3x |

|

إجمالي عرض النطاق الترددي |

1.2 تيرابايت/ثانية |

3 تيرابايت/ثانية |

2.5x |

|

حجم فاي |

11 ملم² |

15 ملم² |

1.4x |

|

قوة فاي |

6 واط |

9 واط |

1.5x |

من المحتمل أن تكون حلول HBM4E القياسية قادرة على استخدام القوالب الأساسية لـ HBM4، على الرغم من أن بعض صانعي الذاكرة قد ينتقلون إلى القوالب الأساسية باستخدام تقنيات المعالجة N5 أو N3P للحصول على أداء وكفاءة أعلى.

C-HBM4E: أول نوع مخصص من الذاكرة للذكاء الاصطناعي والحوسبة عالية الأداء

لقد قام جميع صانعي DRAM الرائدين تقريبًا بتقديم حلول DRAM خاصة بمستويات معينة من التخصيص على مدار العقد الماضي، ولكن لم يكتسب أي منها أي قوة جذب. بدءًا من HBM4E، ستحصل ذاكرة HBM على فرع منفصل من الحلول المخصصة، والتي تم إعدادها لتتميز بقدرات فريدة وواجهات خاصة.

على مستوى عالٍ، C-HBM4E عبارة عن حزمة ذاكرة HBM4E مع قالب أساسي مخصص. تحتفظ المجموعة بأجهزة ذاكرة HBM4E القياسية، والتي تتوافق مع متطلبات الساعة والمتطلبات الكهربائية التي حددتها JEDEC. ومع ذلك، يمكن الآن تخصيص القالب الأساسي بعدة طرق مختلفة، وبالتالي تحويل التركيز من عرض النطاق الترددي الخام إلى دمج المنطق المخصص مباشرةً في أجهزة الذاكرة، وهو ما يمكن تحقيقه باستخدام عدة طرق.

الطريقة الأسهل – التي وصفها Rambus – هي الاحتفاظ بواجهة HBM4E القياسية، جنبًا إلى جنب مع المنطق المخصص المدمج و/أو ذاكرة التخزين المؤقت على القالب الأساسي، لإضافة ميزات أو أداء. طالما أن بروتوكول HBM4E مع دعم البرامج الثابتة ومجموعات البرامج متوافق، فقد يؤدي ذلك إلى زيادة أداء أنظمة الذاكرة الفرعية بما يتجاوز زيادة معدلات النقل أو توسيع الإدخال/الإخراج.

هناك طريقة أكثر تعقيدًا – تصورها TSMC وRambus – وهي وضع وحدة التحكم في الذاكرة HBM4E وواجهة مخصصة للموت مباشرة في القالب الأساسي المنطقي. ينصب جزء كبير من تركيز الصناعة على تقليل عدد الآثار المطلوبة بين المعالج والقالب الأساسي لـ HBM، وستقوم واجهة D2D المخصصة بذلك. من خلال تقليص عرض الواجهة، تستهلك كل حزمة ذاكرة عددًا أقل من منافذ الإدخال/الإخراج، مما يمكّن شريحة SoC واحدة من توصيل عدد أكبر من مكدسات HBM دون زيادة حجم الحزمة أو تعقيدها.

سيسمح القالب المخصص المصنوع باستخدام تقنية N3P الخاصة بـ TSMC بالتعبئة في وحدة تحكم الذاكرة HBM4E، وD2D PHY مخصص، وربما بعض المنطق الإضافي. على سبيل المثال، تتصور KAIST تكامل معالجات حساب الذاكرة القريبة (NMC)، والتي ستجعل على الأقل بعض حلول C-HBM4E نظامًا على الرقائق (SoCs) مزودًا بقدرات المعالجة الأساسية.

إذا تم بالفعل دمج منطق حساب الذاكرة القريبة في C-HBM4E، فيجب أن تتطور حزمة البرامج لتصبح مدركة للهيكل والذاكرة، بدلاً من التعامل مع حزمة C-HBM4E كذاكرة “فقط”. بدون إجراء تغييرات على سلاسل الأدوات وبرامج التشغيل وأوقات التشغيل، تصبح حوسبة الذاكرة القريبة عبارة عن سيليكون غير مرئي – موجود في الأجهزة، ولكنه غير مستخدم بواسطة البرامج.

ستحتاج أنظمة وقت التشغيل والمترجمون إلى معرفة واضحة بهيكل البنك، وموضع القناة، ووحدات التنفيذ في الذاكرة بحيث يمكن جدولة أحمال العمل حيث توجد البيانات فعليًا، بدلاً من نقلها عبر النسيج. بالإضافة إلى ذلك، ستحتاج نماذج البرمجة أيضًا إلى امتدادات للعمل مع الحوسبة داخل الذاكرة، أو أنظمة الذاكرة متعددة الطبقات بشكل عام. أخيرًا، يجب أن تدعم أنظمة التشغيل مجالات الذاكرة غير المتجانسة مع زمن انتقال غير منتظم وتماسك غير متماثل، بينما يجب على المحللين مراقبة التنفيذ الذي يحدث داخل أجهزة الذاكرة وتحسينه.

رؤية أبعد من ذلك

إذا صدقنا الأرقام التي نشرتها TSMC وGUC، فمن المتوقع أن يرتفع أداء HBM الأولي بنحو 2.5 مرة خلال السنوات القليلة المقبلة، وذلك بفضل HBM4E. يفتح هذا التطور الأبواب أمام أنظمة الذاكرة الفرعية بسعة 1 تيرابايت وعرض نطاق ضخم يصل إلى 48 تيرابايت/ثانية. إذا تم اعتماد منطق الحوسبة المخصص داخل القوالب الأساسية لـ HBM من قبل الصناعة، فقد يكون هذا أكبر تحول في كيفية عمل أجهزة الكمبيوتر منذ عقود.

التعليقات