تعد PCI Express (PCIe) تقنية أساسية موجودة منذ عقود، ولن يتغير ذلك في أي وقت قريب. ومن المقرر أن يتغير المعيار ويتطور خلال السنوات القادمة، كما تتمتع التكنولوجيا بتاريخ غني وراءها أيضًا. لقد ورثت PCIe عناصر من معيار PCI الأصلي (مثل مساحة التكوين، وPnP، وBARs، وسجلات الأوامر/الحالة)، وبالتالي فإن تاريخ هذه التقنية يمتد إلى سجلات تاريخ الحوسبة.

منذ تقديمه في عام 2004، ظل PCIe يتطور وفقًا لقاعدة بسيطة: كل مراجعة رئيسية جديدة تضاعف تقريبًا عرض النطاق الترددي للوصلة مع الحفاظ على التوافق مع الإصدارات السابقة. ظلت وتيرة تقديم إصدار PCIe جديد رسميًا كل ثلاث أو أربع سنوات مستقرة في الغالب، باستثناء حدوث انزلاق كبير بين PCIe 3.0 وPCIe 4.0. لكن ما تغير في السنوات الأخيرة ليس الوتيرة، بل صعوبة كل تكرار جديد. قامت الأجيال الأولى بزيادة الإنتاجية دون عناء تقريبًا عن طريق مضاعفة معدلات النقل (الساعات) وتحسين كفاءة التشفير. واليوم، تدفع خارطة الطريق PCIe مباشرة إلى المنطقة التي تحدد فيها تفاوتات التصنيع والمواد وأجهزة إعادة ضبط الوقت ما هو ممكن وتكلفة ذلك.

يستمر المقال أدناه

نظرة سريعة إلى الوراء

بدأت PCIe كبديل للحافلات المشتركة في أوائل العقد الأول من القرن الحادي والعشرين وقدمت اتصالات من نقطة إلى نقطة وعدد حارات قابل للتطوير. يعمل PCIe 1.0 بمعدل نقل بيانات يبلغ 2.5 GT/s لكل حارة، يليه PCIe 2.0 بمعدل 5 GT/s. قام PCIe 3.0 بزيادة معدل البيانات إلى 8 GT/s، وهو ما كان بعيدًا عن مضاعفة الجيل السابق، ولكنه قدم نظام تشفير 128b/130b NRZ أكثر كفاءة، مما قلل بشكل كبير من حمل البروتوكول.

ضاعف PCIe 4.0 معدل النقل إلى 16 GT/s في عام 2017، وكانت هذه هي المرة الأولى التي يتم فيها اعتماد مراجعة PCIe جديدة من قبل أجهزة الكمبيوتر المكتبية من الدرجة المتحمسة بعد عامين فقط من النشر الرسمي للمعيار.

|

المراجعة |

الحد الأقصى لمعدل البيانات |

الترميز |

الإشارة |

|---|---|---|---|

|

PCIe 7.0 (2025) |

128.0 جي تي/ثانية |

1b/1b (وضع الطيران*) |

بام4 |

|

PCIe 6.0 (2022) |

64.0 جي تي/ثانية |

1b/1b (وضع الطيران*) |

بام4 |

|

PCIe 5.0 (2019) |

32.0 جي تي/ثانية |

128ب/130ب |

NRZ |

|

بكيي 4.0 (2017) |

16.0 جي تي/ثانية |

128ب/130ب |

NRZ |

|

بكيي 3.0 (2010) |

8.0 جي تي/ثانية |

128ب/130ب |

NRZ |

|

بكيي 2.0 (2007) |

5.0 جي تي/ثانية |

8ب/10ب |

NRZ |

|

بكيي 1.0 (2003) |

2.5 جيجا/ثانية |

8ب/10ب |

NRZ |

تبع ذلك PCIe 5.0 في عام 2019 بسرعة 32 جيجا بايت/ثانية لكل حارة، وقدم التصميمات الكهربائية لمراكز البيانات إلى أنظمة العملاء، مما يتطلب مواد PCB عالية الجودة وضوابط أكثر صرامة لتكامل الإشارة. الآن، يوفر الناقل ما يصل إلى 128 جيجابايت/ثانية من عرض النطاق الترددي ثنائي الاتجاه من خلال فتحة x16، وهو أمر مبالغ فيه بالنسبة لبطاقات الرسومات الاستهلاكية، ولكنه مفيد بشكل متزايد لمسرعات الذكاء الاصطناعي والتخزين المتطور.

في حين أن اتصال PCIe 5.0 ضروري لمراكز البيانات، إلا أنه لا يدعم كل أجهزة الكمبيوتر الشخصية الاستهلاكية السائدة والمبتدئة PCIe 5.0 لمحركات أقراص SSD وبطاقات الرسومات، مما يسلط الضوء على أن تكلفة التكنولوجيا المقدمة في عام 2019 لا تزال مرتفعة إلى حد ما بالنسبة لأجهزة الكمبيوتر الرخيصة.

PCIe 6.0: نقطة انعطاف

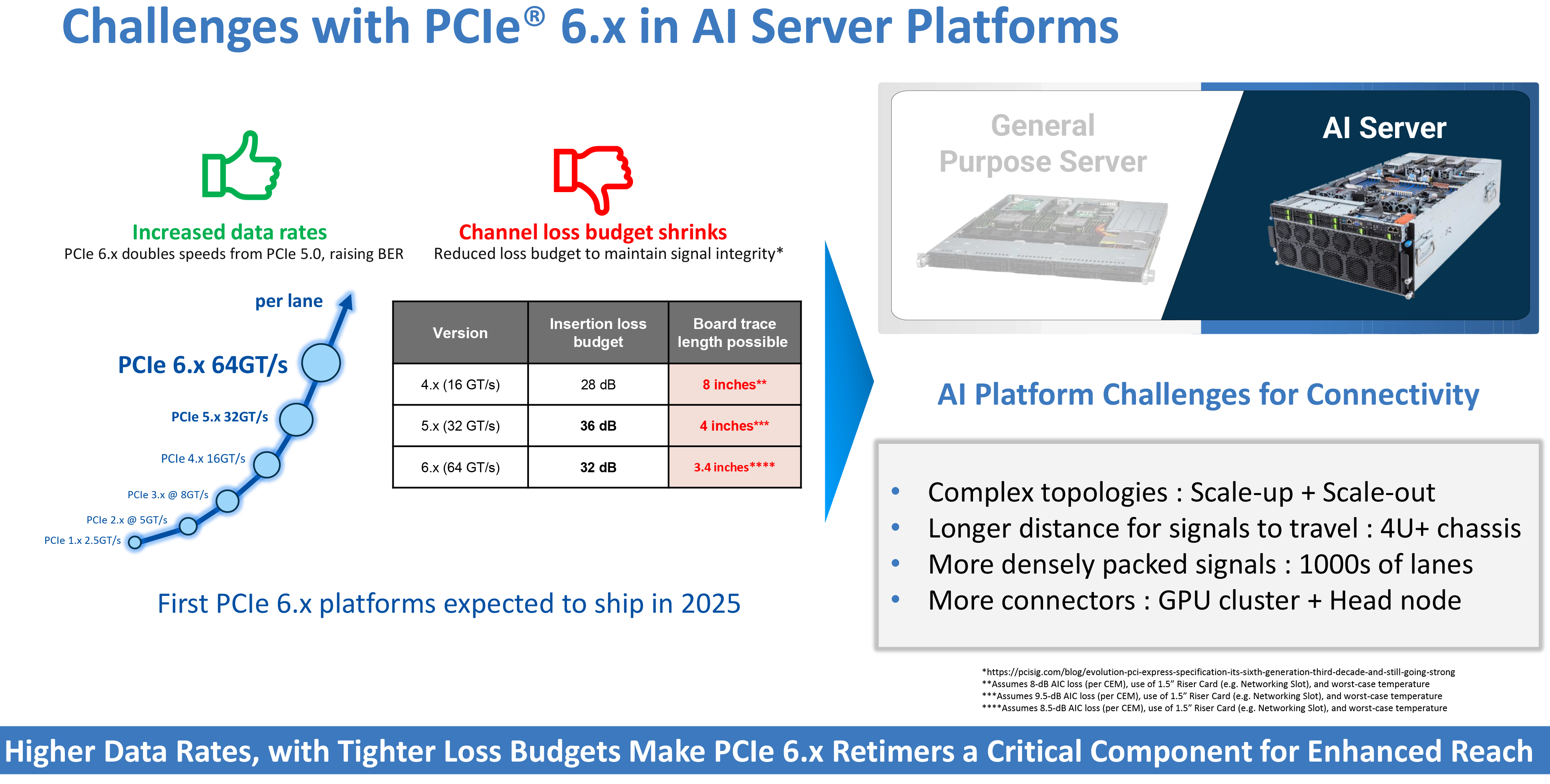

تم طرح PCIe 6.0 في عام 2022، وهو يمثل نقطة انعطاف رئيسية للتكنولوجيا: فبدلاً من دفع الإشارات التقليدية ذات المستويين إلى ترددات أعلى من أي وقت مضى، انتقلت المواصفات إلى PAM4، وهي طريقة تعديل من أربعة مستويات تحمل بتتين لكل رمز، وقدمت تشفير 242B/256B FLIT. يسمح هذا التغيير بمضاعفة الإنتاجية إلى 64 GT/s لكل حارة دون مضاعفة معدل الساعة، ولكنه يأتي مع مقايضات شديدة.

تعمل طرق الإشارات متعددة المستويات مثل PAM4 على ضغط هوامش الجهد بشكل كبير، مما يجعلها أكثر حساسية للضوضاء الكهربائية، والارتعاش، والتداخل بين الممرات، وحتى العيوب الصغيرة في تصنيع ثنائي الفينيل متعدد الكلور، وهو الأمر الذي احتفظ تاريخيًا بطريقة النقل هذه في الشبكات على مستوى المؤسسات مثل 400 جيجابت إيثرنت أو InfiniBand.

للتأكد من أن كل شيء يعمل، فرض PCI-SIG تصحيح الأخطاء الأمامي (FEC) ومعادلة أكثر تعقيدًا بشكل ملحوظ، وهو أمر مكلف من حيث تعقيد السيليكون (يتطلب المزيد من طاقة الحوسبة)، وزمن الوصول الإضافي، والطاقة.

إلى حد كبير، أصبحت وحدات التحكم PCIe 6.0 ذات الواجهات المادية (PHYs) تشبه الآن معالجات الإشارات المختلطة، بدلاً من الواجهات البسيطة، حيث يتعين عليها الآن حزم كتل DSP للمعالجة التناظرية عالية الدقة، والمساواة التكيفية، ومحركات FEC، والتي تستهلك جميعها الطاقة. علاوة على ذلك، أصبحت متطلبات التحقق عبر المنصة أكثر صرامة مع PCIe 6.0 مقارنة بالأجيال السابقة.

وفي الوقت نفسه، من منظور النظام الأساسي، لم يعد القيد الأكبر هو عرض النطاق الترددي أو زمن الوصول؛ إنها المسافة. في PCIe 4.0's 16 GT/s وPCIe 5.0's 32 GT/s، لا يزال بإمكان مصممي النظام توجيه الإشارات عبر آثار اللوحة الأم حتى 11 بوصة في ظل ظروف مناسبة باستخدام مواد عالية الجودة. لم يعد هذا هو الحال مع PCIe 6.0. وفقًا لأرقام فقدان القناة التي نشرتها Astera Labs، يمكن أن يمتد أثر النحاس المباشر الذي يعمل بسرعة 64 جيجا بايت/ثانية إلى ما يصل إلى 3.4 بوصة في ظل ميزانية خسارة تبلغ 32 ديسيبل، اعتمادًا على المواد والظروف.

إلى حد كبير، تعيد هذه القيود تعريف هندسة اللوحة الأم: فالأطوال التي كانت تعتبر تافهة في السابق تتطلب الآن قرارات معمارية، نظرًا لأن عوامل مثل فقدان العزل الكهربائي، وخشونة السطح النحاسي، عبر المعاوقة، وانقطاع الموصل كلها تؤثر على سلامة الإشارة. كما أصبحت الصفائح الاستهلاكية غير كافية، مما يفرض على الشركات المصنعة استخدام مواد عالية التكلفة ومنخفضة الخسارة مخصصة عادة لمعدات الشبكات.

علاوة على ذلك، نظرًا لأن النحاس الخام لم يعد قادرًا على الحفاظ على هوامش الرسم البياني للعين القابلة للاستخدام عبر المسافات العملية، لم تعد أجهزة إعادة ضبط الوقت اختيارية للمسافات ذات المعنى بين مجمع الجذر والفتحة: تستخدم الخوادم الحديثة المزودة بمنفذ PCIe 5.0 ما بين 17 و24 منها، وتم تعيين PCIe 6.0 لرفع هذه التبعية بشكل كبير. على سبيل المثال، يمكن لجهازي إعادة ضبط الوقت لكل رابط توسيع نطاق تتبع PCIe Gen6 إلى 10 بوصات تقريبًا، لكن مواصفات PCIe لا تسمح بأكثر من جهازي إعادة ضبط بين المضيف ونقطة النهاية، لذلك يجب أن يكون مصممو اللوحة الأم للخادم مبدعين.

على الرغم من ذلك، فإن أجهزة إعادة ضبط الوقت ليست حلاً سحريًا: فكل جهاز إعادة ضبط يضيف زمن وصول لا مفر منه، وتكلفة، وعبء التحقق من الصحة، وسحب الطاقة، مما يضيف بسهولة أكثر من 200 واط لكل خادم. يواجه تصميم الموصل ضغوطًا مماثلة. من المتوقع الآن أن تعمل الواجهات المصممة أصلاً للإشارة في نطاق جيجا هرتز المنخفض المكون من رقم واحد بشكل نظيف عند عشرات جيجا هرتز، ولهذا السبب تقدم شركات مثل Molex موصلات جديدة وعائلات كابلات بشكل صريح لـ PCIe 6.0 و7.0. من الواضح أن هذه الموصلات والكابلات باهظة الثمن ومعقدة وأكبر ماديًا مما كانت عليه في PCIe 4.0 مرات.

ونظرًا لجميع التعقيدات المحيطة بـ PCIe 6.0، يقول والاس سي. كو، الرئيس التنفيذي لشركة Silicon Motion، إنه لا يتوقع أن تصبح محركات أقراص الحالة الصلبة (SSD) المخصصة للمستهلكين والمزودة بواجهة PCIe 6.0 منتجًا معتمدًا على نطاق واسع قبل عام 2030.

PCI 7.0، 8.0 وما بعده

وبعيدًا عن PCIe Gen 6، تظل خريطة الطريق متسقة من حيث الإيقاع وزيادة الأداء، ولكن ليس من حيث إيقاع التنفيذ والاعتماد من قبل الصناعة. يستهدف PCIe 7.0 أداءً آخر يتضاعف إلى 128 GT/s لكل حارة، ولكن هذه المرة يؤدي في الواقع إلى زيادة الساعات وتحسين نظام تعديل PAM4 وتشديد التفاوتات الكهربائية.

|

مراجعة PCIe |

معدل البيانات (GT/s) |

×1 |

×2 |

×4 |

x8 |

×16 |

|---|---|---|---|---|---|---|

|

بكيي 1.x + |

2.5 |

500 ميجابايت/ثانية |

1 جيجابايت/ثانية |

2 جيجابايت/ثانية |

4 جيجابايت/ثانية |

8 جيجابايت/ثانية |

|

بكيي 2.x + |

5 |

1 جيجابايت/ثانية |

2 جيجابايت/ثانية |

4 جيجابايت/ثانية |

8 جيجابايت/ثانية |

16 جيجابايت/ثانية |

|

بكيي 3.x + |

8 |

2 جيجابايت/ثانية |

4 جيجابايت/ثانية |

8 جيجابايت/ثانية |

16 جيجابايت/ثانية |

32 جيجابايت/ثانية |

|

بكيي 4.x + |

16 |

4 جيجابايت/ثانية |

8 جيجابايت/ثانية |

16 جيجابايت/ثانية |

32 جيجابايت/ثانية |

64 جيجابايت/ثانية |

|

بكيي 5.x + |

32 |

8 جيجابايت/ثانية |

16 جيجابايت/ثانية |

32 جيجابايت/ثانية |

64 جيجابايت/ثانية |

128 جيجابايت/ثانية |

|

بكيي 6.x + |

64 |

16 جيجابايت/ثانية |

32 جيجابايت/ثانية |

64 جيجابايت/ثانية |

128 جيجابايت/ثانية |

256 جيجابايت/ثانية |

|

بكيي 7.x + |

128 |

32 جيجابايت/ثانية |

64 جيجابايت/ثانية |

128 جيجابايت/ثانية |

256 جيجابايت/ثانية |

512 جيجابايت/ثانية |

|

بكيي 8.x + |

256 |

64 جيجابايت/ثانية |

128 جيجابايت/ثانية |

256 جيجابايت/ثانية |

512 جيجابايت/ثانية |

1 تيرابايت/ثانية |

يهدف PCIe 8.0، الذي لا يزال قيد التطوير، إلى مضاعفة ذلك مرة أخرى إلى 256 جيجا بايت / ثانية مع المواصفات المتاحة في وقت ما في عام 2028. إذا تم تحقيقه، فإن اتصال x16 سيقترب من ما يقرب من 1 تيرابايت / ثانية من عرض النطاق الترددي المجمع في كلا الاتجاهين. ما إذا كانت هذه السرعات ستظل قابلة للتطبيق على النحاس هو سؤال مفتوح. يقوم بائعو الموصلات بالفعل بتطوير أجهزة متخصصة، بما في ذلك الكابلات الممتدة والمآخذ عالية الكثافة، لاستيعاب معدلات البيانات المستقبلية. لم تعد الوصلات الضوئية وتصميمات PHY المعبأة بشكل مشترك بمثابة تمارين أكاديمية ويمكن أن تصبح متطلبات في مرحلة ما، على الرغم من أن Al Yanes، رئيس PCI-SIG، يشير إلى أن المنظمة تتطلع إلى تمكين سرعة تبلغ 256 جيجا بايت / ثانية على النحاس. الوقت وحده سيكون قادرًا على معرفة ما إذا كان ذلك سيصبح حقيقة.

مستقبل PCIe: أداء يمكن التنبؤ به، وتطلب السيليكون

أحد الأسئلة البارزة حول تطور تقنيات PCI وPCIe هو ما الذي يميزها في أجزاء مختلفة من تاريخها. بدأت إنتل في تطوير PCI لأجهزة الكمبيوتر المكتبية في عام 1990، ولم تتصور دخولها إلى مساحة الخادم إلا في منتصف التسعينيات. ومع ذلك، بحلول الوقت الذي دخلت فيه PCIe المشهد، كانت شركة Intel تهيمن على سوق الخوادم في وقت مبكر من الألفية الجديدة.

تم تصميم كل من PCI وPCIe في الأصل مع وضع أجهزة الكمبيوتر في الاعتبار، حيث نمت مبيعات أجهزة الكمبيوتر الشخصية بوتيرة عالية في التسعينيات وأوائل عام 2010، مما أدى إلى زيادة مبيعات بطاقات الرسومات المتعطشة للنطاق الترددي والتي كانت (ولا تزال) إلزامية لألعاب الفيديو. وعلى مدى السنوات التالية، ازدهر نمو البنية التحتية السحابية، الأمر الذي تطلب مجموعة من القدرات والتكاليف الخاصة بها. اليوم، تهيمن البنية التحتية للذكاء الاصطناعي، وتحدد أهدافًا جديدة للأداء والقدرات.

بشكل عام، لا تزال خارطة طريق PCIe تعد بنمو أداء يمكن التنبؤ به. ولكن بالنظر إلى التطبيق الذي يقود عالم تكنولوجيا المعلومات الآن، فإن الحفاظ على هذا النمط يتطلب الآن زيادات هائلة في الجهد الهندسي. تؤدي معدلات البيانات الأعلى إلى تقصير مسافات التتبع، وزيادة تكاليف اللوحة، وتتطلب سيليكونًا أكثر نشاطًا للحفاظ على سلامة الإشارة. ولكن في الوقت نفسه، قم بإنجاز المزيد من العمل في أي ثانية معينة، وبالتالي زيادة كفاءة الأداء إلى الحد الأقصى.

ومع ذلك، سواء ظلت الأجيال القادمة تعمل بالكهرباء أو انتقلت نحو البصريات، فإن PCI Express لم يعد اختياريًا؛ إنه العمود الفقري الهيكلي لأنظمة الحوسبة الحديثة، بدءًا من جهاز كمبيوتر متواضع وصولاً إلى Colossus الخاص بـ Elon Musk مع مئات الآلاف من وحدات معالجة الرسومات Nvidia.

التعليقات