قامت شركة Rebellions، وهي شركة مصممة لمسرعات استدلال الذكاء الاصطناعي من كوريا الجنوبية، مؤخرًا بتفصيل مسرع Rebel 100 AI متعدد الشرائح الذي يعتمد على تقنية Unified Chiplet Interconnect Express (UCIe) في المؤتمر الدولي لأشباه الموصلات ذات الحالة الصلبة (ISSCC). يعد المعالج واحدًا من أولى التصميمات متعددة الشرائح في الصناعة التي تعتمد على وصلات UCIe-A لدمج أربع شرائح صغيرة معًا.

تمثل التصميمات متعددة الشرائح مستقبل مسرعات الذكاء الاصطناعي والحوسبة عالية الأداء عالية الأداء، حيث أن الطلب على الأداء يفوق بكثير قدرة المسابك على توسيع نطاق تقنيات العمليات الخاصة بها. لقد أدرك كبار مطوري وحدات المعالجة المركزية ووحدات معالجة الرسومات مثل AMD وIntel وNvidia قيمة التصميمات متعددة الشرائح وأحدث منتجاتهم تتبنى المنهجية بالكامل.

يهدف النهج المتوافق مع معايير الصناعة للاتصالات البينية متعددة الشرائح – واجهة UCIe – إلى تمكين النطاق الترددي العالي والتوصيل البيني بزمن انتقال منخفض بين الشرائح الصغيرة. ومع ذلك، حتى الآن، كان المعيار خاضعًا لاعتماد بطيء، مما يجعل ورقة ISSCC 2026 الصادرة عن Rebellions أكثر قيمة.

The Rebel 100: شريحة رباعية، مسرع 2 FP8 PFLOPS في لمحة سريعة

إن Rebellions Rebel100 عبارة عن مسرع ذكاء اصطناعي مكون من أربع شرائح تم تصميمه لاستدلال نماذج اللغة الكبيرة التي تعتمد تصميمًا متعدد الشرائح لزيادة إنتاجية القالب والأداء إلى أقصى حد، لتوفير التوازن الصحيح بين السعر والإنتاجية في النهاية.

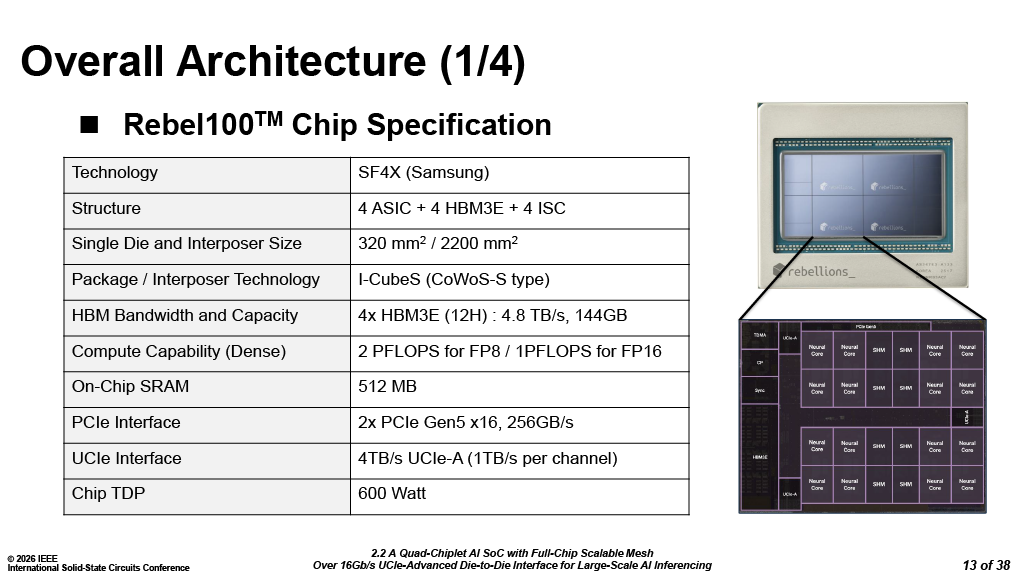

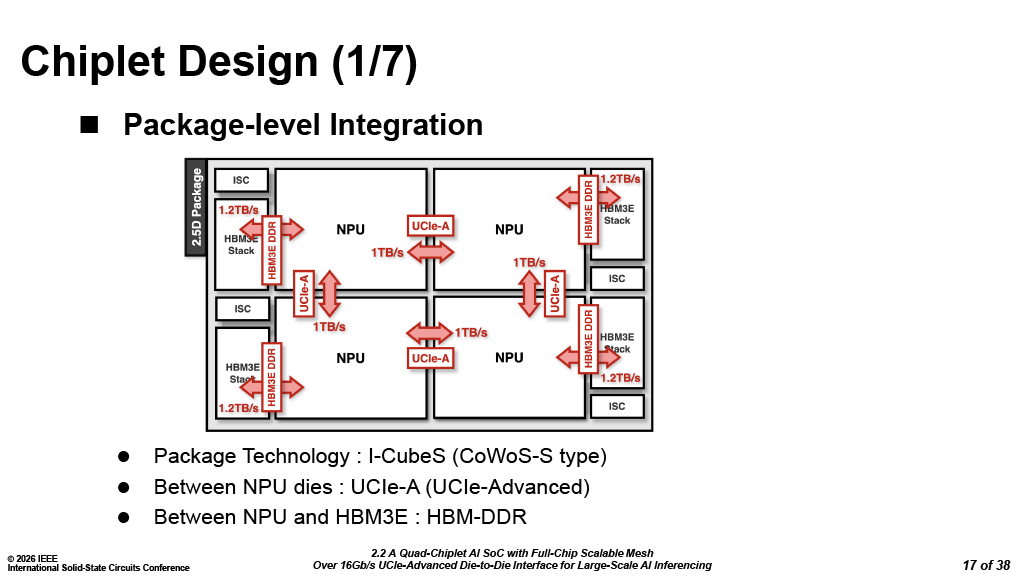

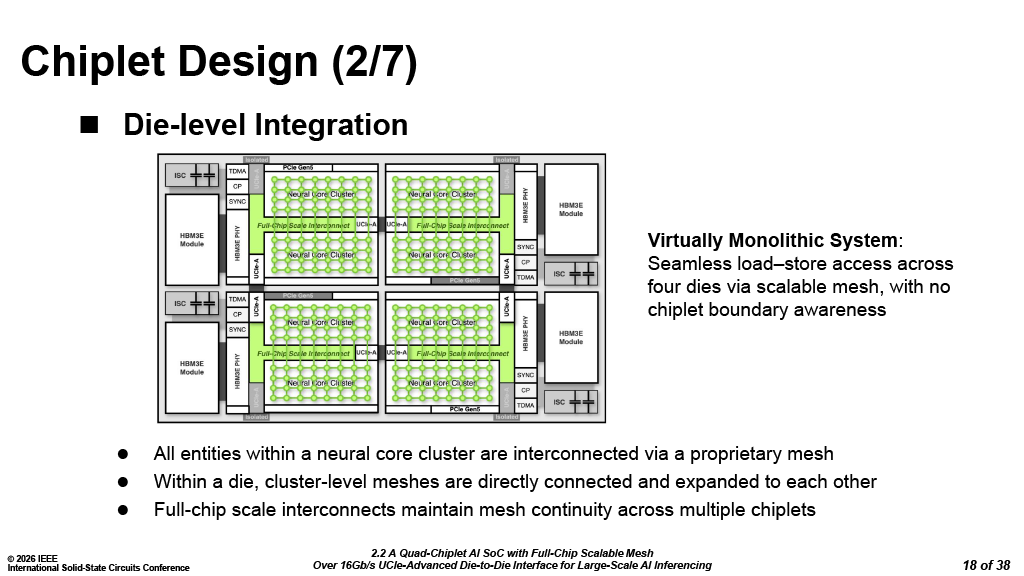

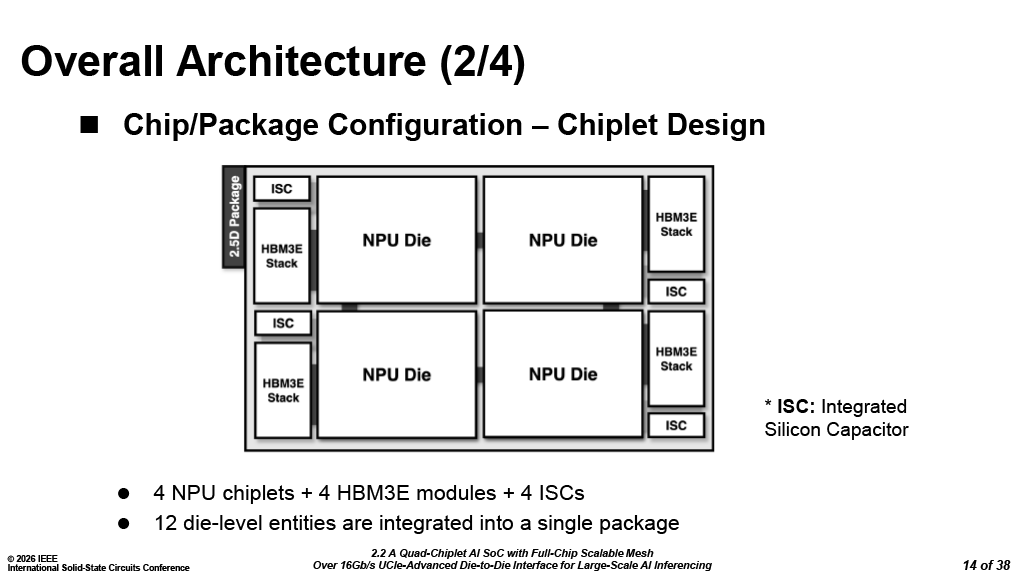

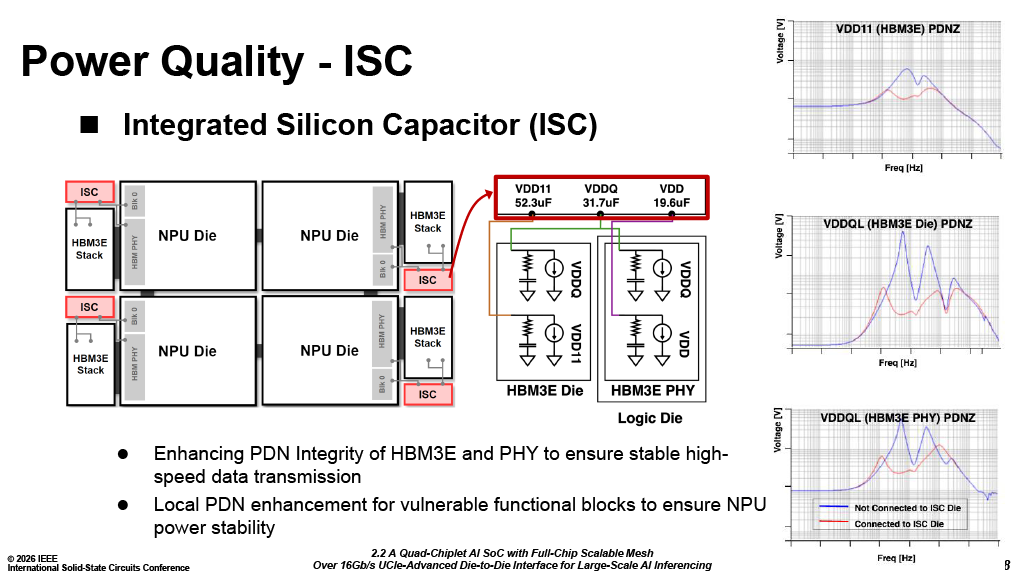

يتكون نظام Rebel 100 المدمج (SiP) من أربعة 320 مم2 تموت وحدة المعالجة العصبية (NPU)، كل منها مجهزة بمجموعة ذاكرة 12Hi HBM3E سعة 36 جيجابايت (لمدة 144 ميجابايت من HBM3E لكل حزمة) ومترابطة باستخدام طوبولوجيا شبكية مع بعضها البعض. يتم تصنيع قوالب NPU باستخدام تقنية معالجة SF4X المحسّنة للأداء من سامسونج ويتم تعبئتها باستخدام طريقة التغليف المتقدمة I-CubeS (CoWoS-S–class) من سامسونج باستخدام وسيط. ولأسباب تتعلق بسلامة الطاقة، يتميز SiP أيضًا بأربعة قوالب مكثف سيليكون مدمجة (ISC) تعمل أيضًا للأغراض الميكانيكية.

يتم ربط الشرائح الصغيرة ببعضها البعض باستخدام واجهة UCIe-Advanced die-to-die التي تعمل بسرعة 16 جيجابت في الثانية وتوفر نطاق ترددي مجمع يبلغ 4 تيرابايت/ثانية. يحقق الاتصال البيني زمن وصول يصل إلى 11ns تقريبًا من Flit-Aware Die-to-Die (FDI) إلى FDI، مما يعمل على توسيع دلالات تحميل الذاكرة وتخزينها بشفافية عبر الشرائح الصغيرة لتمكين SiP من العمل كمعالج واحد، بدلاً من مجموعة من القوالب المنفصلة.

على جانب النظام، يتصل Rebel100 بالمضيفين عبر واجهتي PCIe 5.x x16 التي تدعم SR-IOV وتشغيل نظير إلى نظير.

يمكن لـ One Rebel 100 SiP تقديم أداء 2 FP8 PFLOPS أو 1 FP16 PFLOPS دون تناثر عند 600 واط، وهو ما يتماشى مع ما يمكن أن تقدمه Nvidia's H200 عند 700 واط. تدعي Rebellions أيضًا أن الوحدة يمكنها تحقيق 56.8TPS على LLaMA v3.3 70B مع تسلسل إدخال/إخراج دفعة واحدة 2k/2k، على الرغم من أن هذه هي الأرقام من البائع نفسه، وليس من مختبر مستقل. علاوة على ذلك، تركز القصة على الكشف عن كيفية عمل أحد مسرعات الذكاء الاصطناعي الأولى المستندة إلى شرائح UCIe.

تضع الشركة حزمة Rebel 100 رباعية الشرائح كوحدة أساسية للأنظمة المتقاطعة والأنظمة على مستوى الحامل القادرة على دعم نماذج تريليون معلمة وسياقات مليون رمز مميز. لذلك، في حين أنه من غير الواضح ما إذا كانت Rebellions تخطط لبناء SiPs أكبر باستخدام الشرائح الصغيرة الموجودة. لكنها تتصور بالتأكيد أن شركائها يبنون مجموعات واسعة النطاق وواسعة النطاق تحتوي على عشرات إلى عشرات الآلاف من مسرعات الذكاء الاصطناعي.

المتمردين 100 NPU وحركة البيانات

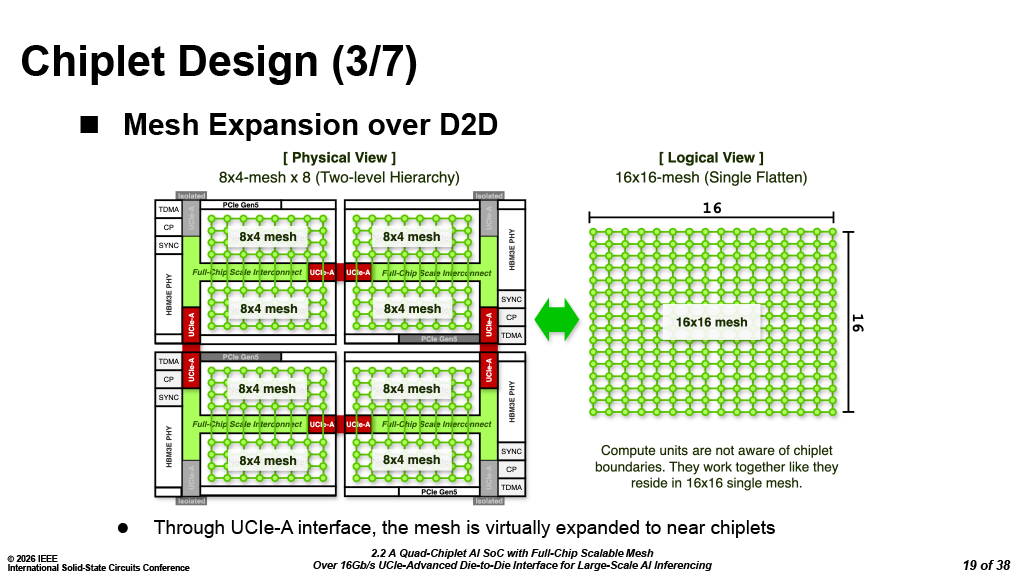

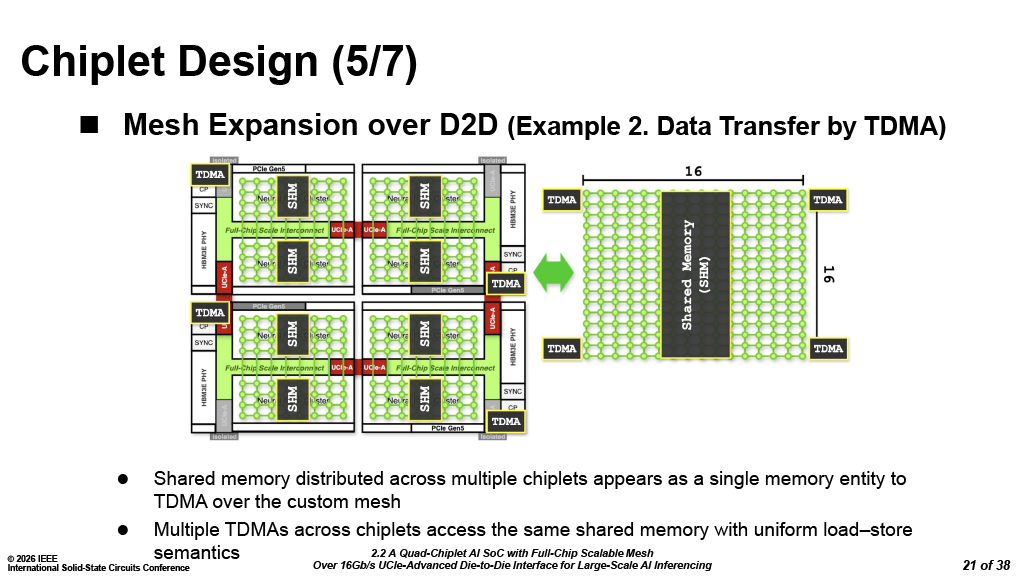

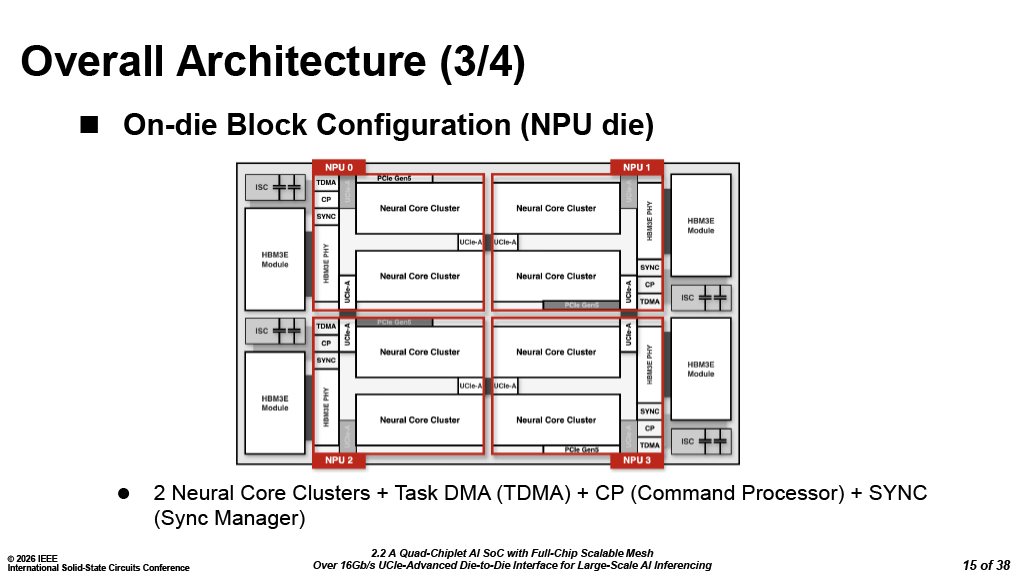

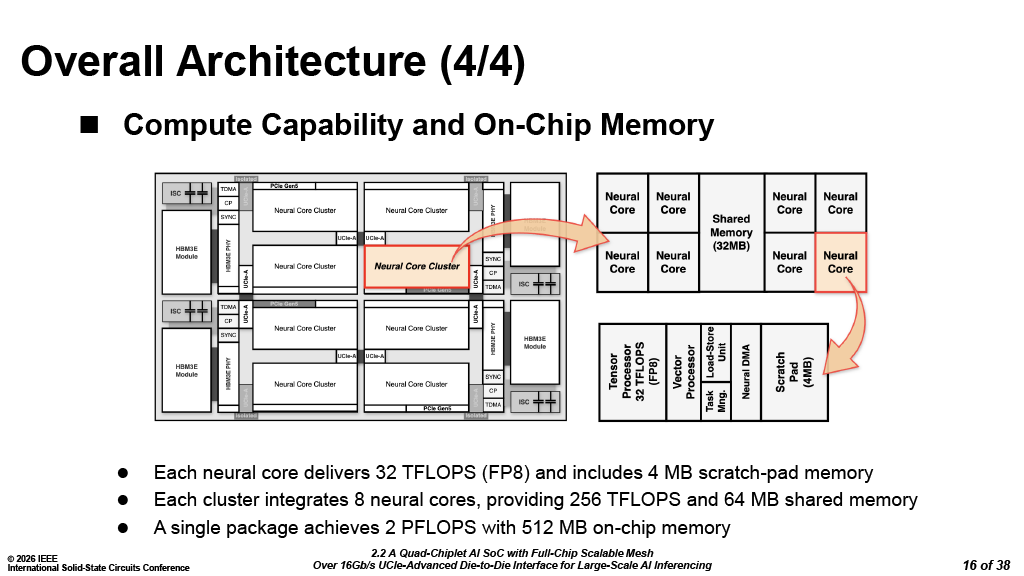

تدمج كل شريحة صغيرة مجموعتين عصبيتين أساسيتين، تحتوي كل منهما على ثمانية نوى عصبية و32 ميجابايت من الذاكرة المشتركة. وفقًا لورقة ISSCC، يتم تقسيم الذاكرة المشتركة إلى 16 شريحة وتتميز بعرض نطاق ترددي إجمالي يبلغ 64 تيرابايت/ثانية، وتحتوي الشريحة الصغيرة على 64 جهاز توجيه تشكل طوبولوجيا شبكية حبيبية 8 × 4 مع ثلاث قنوات منفصلة منطقيًا: البيانات (D)، والطلب (R)، والتحكم (C). بالإضافة إلى ذلك، يحتوي كل SiP على 256 ميجابايت من ذاكرة المسودة (بسرعة 128 تيرابايت/ثانية).

تستخدم الشبكة ثنائية الأبعاد (NoC) الموجودة على الرقاقة نظام توجيه XY مباشر، بحيث تنتقل الحزم أولاً على طول محور واحد ثم المحور الآخر، مع تطبيق قيود الدوران لتجنب حالات التوقف التام. يتم التعامل مع التحكيم داخل أجهزة التوجيه باستخدام آلية مرجحة، بحيث تتم خدمة حركة المرور من مصادر مختلفة بشكل عادل، ولكن مع أولوية قابلة للتعديل. يمكن تعديل أوزان جودة الخدمة في وقت التشغيل لجعل النظام يفضل أنواعًا معينة من حركة المرور اعتمادًا على ما إذا كان عبء العمل ثقيلًا على الحوسبة أو كثيف الذاكرة.

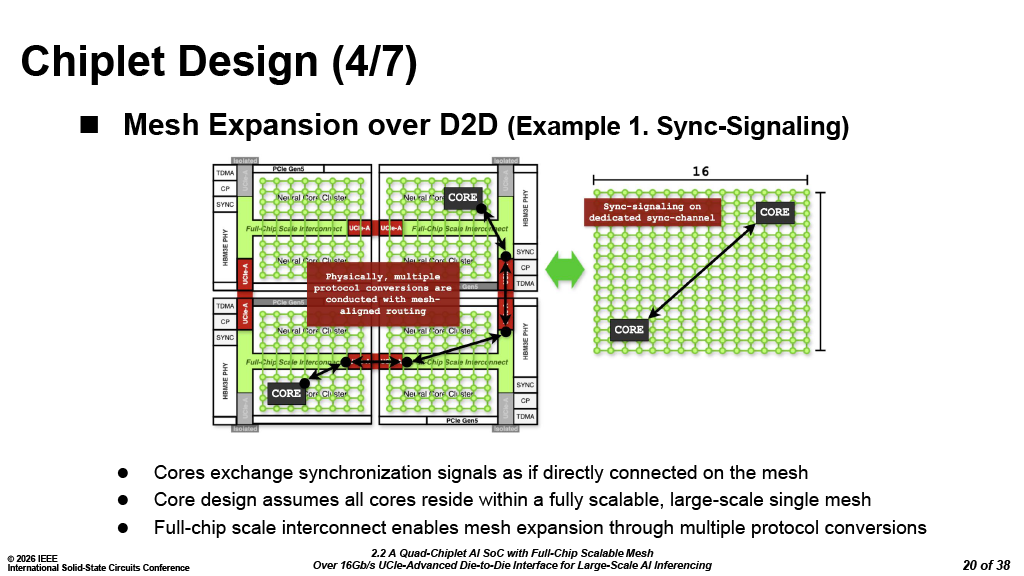

تتوسع شبكة NoC ثنائية الأبعاد الموجودة داخل كل شريحة بشكل منطقي عبر UCIe، وبالتالي فإن النظام رباعي الشرائح الكامل الموجود في الحزمة يتصرف مثل معالج كبير متصل بالشبكة على المستوى المنطقي. مع الأخذ في الاعتبار زمن الوصول المنخفض من شريحة إلى شريحة (أو بالأحرى زمن انتقال الاستثمار الأجنبي المباشر إلى الاستثمار الأجنبي المباشر)، فإن هذا يبسط الحياة لمطوري البرامج إلى حد كبير. ومن المثير للاهتمام، في حين أن جميع الشرائح تتميز بثلاث واجهات UCIe-A لتعدد الاستخدامات (أو ربما التكرار؟)، فإن التكوين الكامل يتسع إلى 256 جهاز توجيه عبر الشبكة بأكملها، لذلك يبقى أن نرى ما إذا كان بإمكان Rebellions بناء مسرعات بأكثر من أربع شرائح باستخدام البنية الحالية.

على الرغم من أن مواصفات UCIe 1.0 تتضمن تعيينات لبروتوكولات CXL.io وCXL.mem وCXL.cache أعلى اتصال PCIe 6.0، إلا أن هذه تعيينات بروتوكول اختيارية وليست متطلبات إلزامية. تدعم المواصفات أيضًا بروتوكولات البث ودلالات الذاكرة المحددة من قبل البائع، وهو بالضبط ما فعلته Rebellions مع Rebel 100.

قامت شركة Rebellions ببناء محرك قوي لحركة البيانات للحفاظ على تغذية تصميمها رباعي الشرائح. يدمج كل قالب NPU نظام فرعي DMA قابل للتكوين مع ثمانية محركات تنفيذ يمكنها سحب البيانات من HBM3E المحلي، أو HBM3E البعيد الموجود على شريحة صغيرة أخرى، أو من الذاكرة المشتركة الموزعة. يمكن أن يصل عرض النطاق الترددي لكل DMA إلى 2.6 تيرابايت/ثانية، وهو ما يكفي لمسرع يركز على الاستدلال. وفي الوقت نفسه، لمنع مهام معينة من تجويع المهام الأخرى، نفذت الشركة ضوابط جودة الخدمة على مستوى المهمة المصممة لتقليل زمن الوصول الطويل وتجنب الازدحام عند تشغيل أعباء عمل مختلفة في وقت واحد.

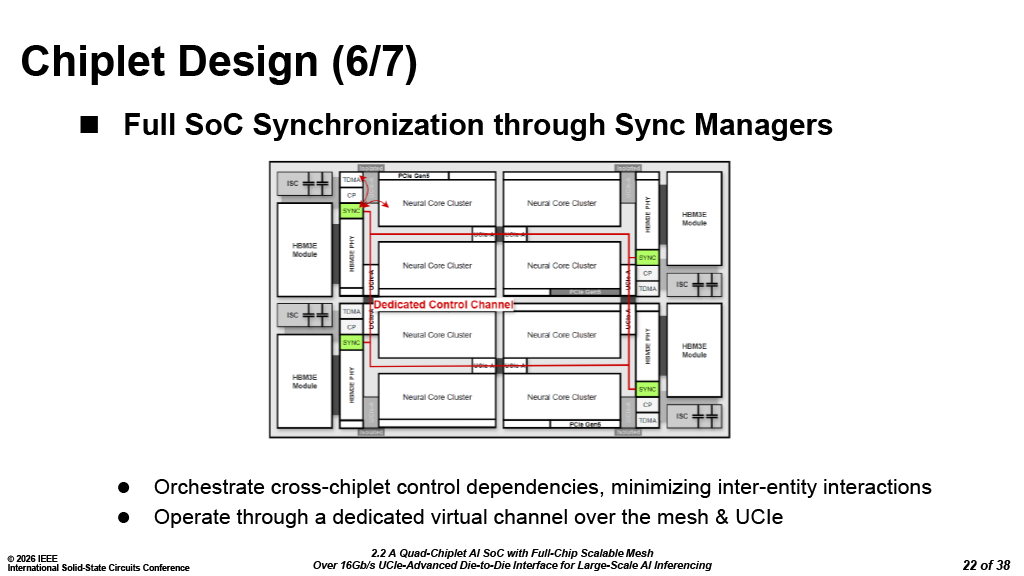

يتطلب تنسيق العمل عبر أربع شرائح صغيرة مزامنة دقيقة. ولكن بدلاً من الاعتماد على برنامج جدولة مخصص، قامت Rebellions بتطبيق مديري المزامنة في كل وحدة NPU بدلاً من ذلك. تدمج كل شريحة صغيرة مديرًا مخصصًا لمزامنة الأجهزة مع منطق تحكم متصل يمكنه تنسيق النشاط عبر القوالب، إما تحت تحكم مركزي أو بطريقة أكثر استقلالية. تتجنب البنية على وجه التحديد الاتصالات المباشرة من نظير إلى نظير بين الوحدات والتبعيات بين الوحدات لتقليل حركة المرور والتنسيق غير الضرورية والحفاظ على الاستخدام العام مرتفعًا خلال مراحل التنفيذ المختلفة لاستدلال LLM.

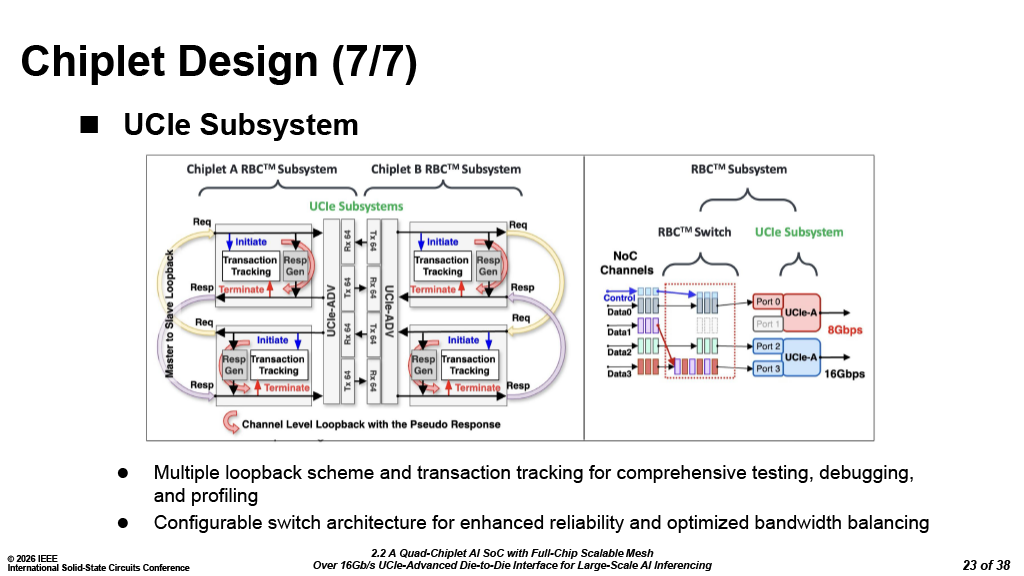

لتحسين موثوقية واجهة القالب، بالإضافة إلى وظائف UCIe القياسية، نفذت Rebellions أوضاع استرجاع متعددة، وتتبع مستوى المعاملة، وتشخيصات على مستوى القناة، والتي تهدف عمومًا إلى تبسيط التحقق من الصحة وعزل الأخطاء في حزمة متعددة القوالب أثناء تصحيح الأخطاء. بالنسبة لعمليات النشر التجاري، أضافت Rebellions وضع تبديل قابل للتكوين يستخدم الميزات المذكورة أعلاه للتضحية بكمية صغيرة من الأداء مقابل تحسين خصائص MTBF وMTTF لزيادة وقت التشغيل إلى أقصى حد، وهو أمر مهم لمجموعات الذكاء الاصطناعي الكبيرة حيث يهم وقت التشغيل أكثر من مكاسب الإنتاجية الهامشية.

نهج غير تقليدي لتوصيل الطاقة

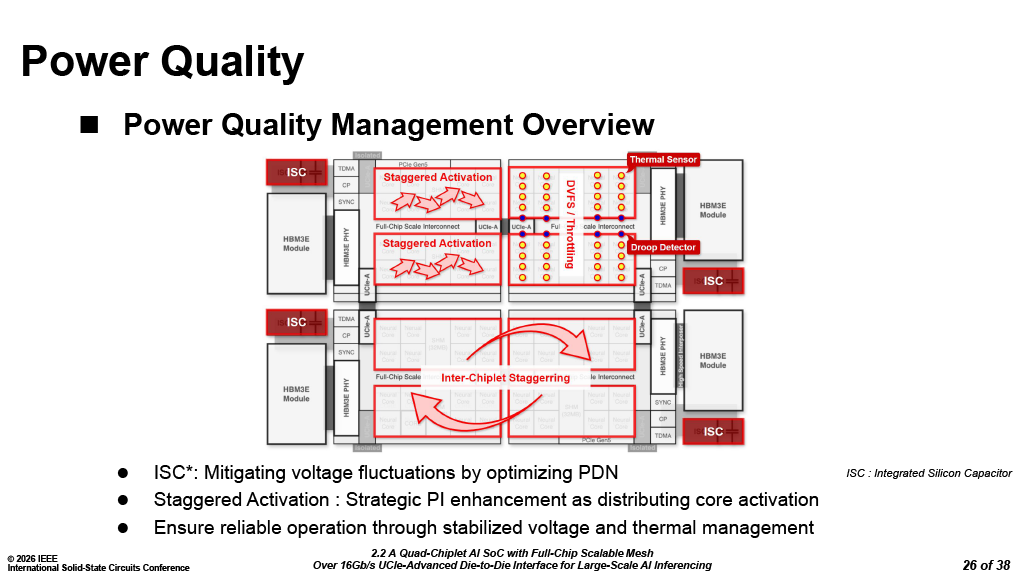

تم تصنيف مسرع Rebel 100 من حيث قوة التصميم الحراري البالغة 600 واط TDP، ولكن الزيادات العابرة اللحظية – عند تشغيل النوى العصبية المتعددة – تتجاوز المستوى الاسمي بمقدار مرتين. مع ارتفاع التيارات بسرعة وبشكل حاد، فإنها تؤدي إلى انخفاضات في الجهد، مما يشكل تحديات كبيرة لسلامة الطاقة في مسرع الذكاء الاصطناعي رباعي الشرائح.

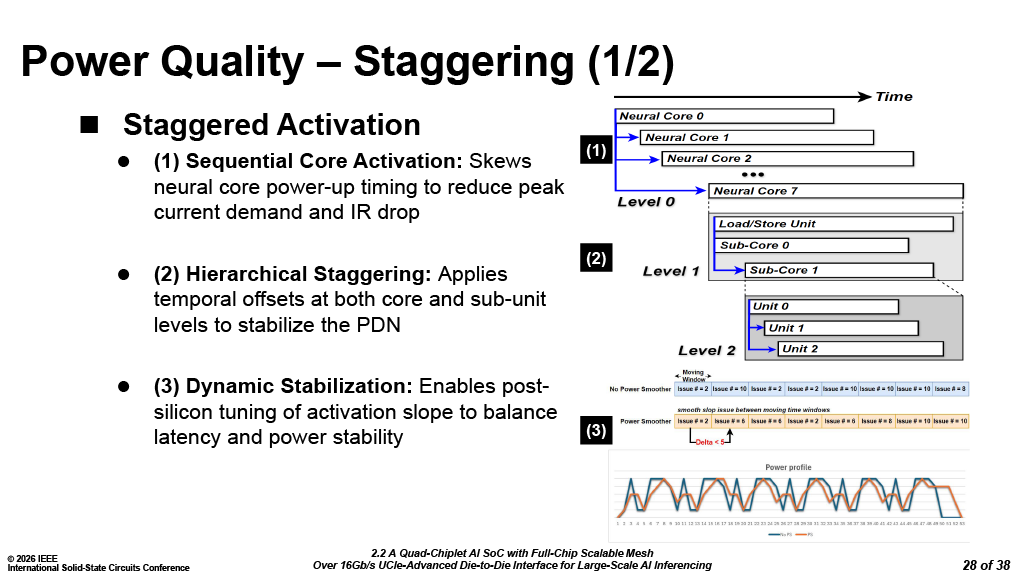

وللتخفيف من ذلك، طبقت Rebellions تقنية مذهلة للأجهزة تعمل على تعويض أوقات بدء النوى العصبية بدلاً من تنشيطها في وقت واحد، مما يعمل على تسهيل المنحدرات الحالية وتقليل ضوضاء العرض. تظهر القياسات أن التبديل المتزامن ينتج عنه ارتفاع حاد في التيار واضطراب ملحوظ في الجهد، في حين أن التنشيط المتدرج يؤدي إلى تحولات ألطف وسكك طاقة أكثر استقرارًا، وفقًا لـ Rebellions. يحد منطق التحكم الإضافي ديناميكيًا من معدل إصدار التعليمات خلال فترات زمنية قصيرة لتقليل تغيرات الحمل المفاجئة بشكل أكبر داخل الشريحة الصغيرة وعبر القوالب.

تضيف حركة الذاكرة طبقة أخرى من الضغط. يمكن أن تكون تدفقات HBM3E بنفس القدر من المتطلبات مثل الزيادات الحسابية، مما يضع ضغطًا إضافيًا على شبكة توصيل الطاقة. ولتعزيزها، أضافت Rebellions قالبًا مخصصًا لمكثف السيليكون المدمج (ISC) الذي يتضمن السعة الموزعة عبر قضبان VDD لخدمة كل من NPU وHBM3E PHY. يعمل هذا الأسلوب على تقليل تذبذبات الجهد بشكل أكبر وتقليل قمم المعاوقة مقارنة بالتصميم الذي لا يحتوي على قوالب ISC.

مثال قوي لتصميم متعدد الشرائح

مع أول مسرع استدلال يعمل بالذكاء الاصطناعي متعدد الشرائح Rebel 100، تمكنت Rebellions من تحقيق أداء مماثل لأداء Nvidia's H200 بطاقة أقل، وإن كان ذلك مع استهلاك أعلى بكثير من السيليكون. الإنجاز الأكبر للشركة هو Rebel 100 SiP، وهو أحد أول المسرعات متعددة الشرائح في الصناعة التي تستخدم وصلات UCIe-A.

بدلاً من بناء قالبين كبيرين بحجم شبكاني، اختارت شركة Rebellions تصميمًا رباعي الشرائح بأربع قوالب مقاس 320 مم2 يسهل تطويرها وإنتاجها، لا سيما مع الأخذ في الاعتبار نهج سامسونج الذي لا يحتوي على حبيبات تجاه الأشعة فوق البنفسجية (EUV) والذي لا يفضل بشكل خاص القوالب الكبيرة. لجعل تصميم الشرائح الرباعية يعمل بسلاسة، طورت Rebellions شبكة شبكية داخلية ثنائية الأبعاد على الرقاقة تتوسع بشكل منطقي إلى ما وراء حدود الشرائح الصغيرة عبر UCIe بحيث يتصرف نظام الشرائح الرباعية الكامل في الحزمة مثل معالج واحد كبير متصل بالشبكة.

لتحسين تصميمها بشكل أكبر، لم تعتمد Rebellions البروتوكولات القياسية المستندة إلى CXL ولكنها نفذت نظام DMA الفرعي القابل للتكوين ومديري المزامنة. علاوة على ذلك، ولضمان سلامة الطاقة، فقد طبقت تقنية مذهلة للأجهزة تعمل على تسهيل المنحدرات الحالية وتقليل ضوضاء العرض. علاوة على ذلك، أضافت الشركة قالب مكثف السيليكون المدمج (ISC) لتخفيف تقلبات الجهد وتقليل قمم المعاوقة.

على الرغم من عدم استخدام مواصفات UCIe 1.0 إلى أقصى حد، فإن Rebel 100 يمثل مثالًا جيدًا لتصميم متعدد الشرائح يعتمد على التوصيل البيني المتوافق مع معايير الصناعة مع الاستمرار في استخدام تقنيات خاصة لتحقيق أقصى قدر من الأداء وتحسين قوة النظام الموجود في الحزمة.

التعليقات