JEDEC، المنظمة المسؤولة عن تحديد مواصفات أنواع الذاكرة القياسية الصناعية، على وشك الانتهاء من SPHBM4، وهو معيار ذاكرة جديد مصمم لتوفير عرض نطاق كامل من فئة HBM4 مع واجهة “ضيقة” 512 بت، وقدرات أعلى، وتكاليف تكامل أقل من خلال الاستفادة من التوافق مع الركائز العضوية التقليدية. إذا انطلقت التكنولوجيا، فسوف تعالج العديد من الفجوات في الأسواق التي يمكن أن تخدمها HBM، ولكن كما سنوضح أدناه، من غير المحتمل أن تكون قاتلة لذاكرة GDDR.

على الرغم من أن واجهات الذاكرة ذات النطاق الترددي العالي (HBM) 1024 بت أو 2048 بت تتيح أداءً لا مثيل له وكفاءة في استخدام الطاقة، إلا أن هذه الواجهات تستهلك الكثير من عقارات السيليكون الثمينة داخل المعالجات المتطورة، مما يحد من عدد مكدسات HBM لكل شريحة وبالتالي سعة الذاكرة المدعومة بمسرعات الذكاء الاصطناعي، مما يؤثر على كل من أداء المسرعات الفردية وكذلك قدرات المجموعات الكبيرة التي تستخدمها.

HBM في حزمة “قياسية”.

تعالج ذاكرة الحزمة القياسية ذات النطاق الترددي العالي (SPHBM4) هذه المشكلة عن طريق تقليل عرض واجهة ذاكرة HBM4 من 2048 بت إلى 512 بت مع تسلسل 4:1 للحفاظ على نفس عرض النطاق الترددي. لم تحدد JEDEC ما إذا كان “التسلسل 4:1” يعني مضاعفة معدل نقل البيانات أربع مرات من 8 GT/s في HBM4، أو تقديم نظام تشفير جديد بساعات أعلى. ومع ذلك، فإن الهدف واضح: الحفاظ على النطاق الترددي الإجمالي لـ HBM4 بواجهة 512 بت.

في الداخل، ستستخدم حزم SPHBM4 قالبًا أساسيًا متوافقًا مع معايير الصناعة (من المحتمل أن يكون مصنوعًا بواسطة مسبك باستخدام عملية تصنيع منطقية وبالتالي ليس أرخص حيث أن توجيه دوائر DRAM “الواسعة” إلى قالب قاعدة “ضيق” من المحتمل أن يصبح سيئًا هنا من حيث الكثافة وستكون هناك تحديات في تسجيل الوقت بسبب الأسلاك البطيئة من DRAMs والأسلاك السريعة من القالب الأساسي نفسه). كما أنها ستستخدم قوالب HBM4 DRAM القياسية، مما يبسط تطوير وحدة التحكم (على الأقل على المستوى المنطقي) ويضمن بقاء السعة لكل حزمة على قدم المساواة مع HBM4 وHBM4E، حتى 64 جيجابايت لكل حزمة HBM4E.

على الورق، يعني هذا مضاعفة سعة ذاكرة SPHBM4 أربع مرات مقارنة بـ HBM4، ولكن من الناحية العملية، من المرجح أن يوازن مطورو شرائح الذكاء الاصطناعي بين سعة الذاكرة وقدرة حوسبة أعلى وتعدد الاستخدامات التي يمكنهم تعبئتها في شرائحهم، حيث تصبح عقارات السيليكون أكثر تكلفة مع كل تقنية معالجة جديدة.

قاتل GDDR7؟

من المحتمل أن يتساءل القارئ المتعطش عن سبب عدم استخدام ذاكرة SPHBM4 مع وحدات معالجة الرسومات وبطاقات الرسومات الخاصة بالألعاب، والتي يمكن أن تتيح عرض نطاق ترددي أعلى بزيادة معتدلة في التكلفة مقارنةً بـ GDDR7 أو GDDR7X المحتمل مع تشفير PAM4.

تم تصميم SPHBM4 لتوفير عرض النطاق الترددي من فئة HBM4، بشكل أساسي لإعطاء الأولوية للأداء والسعة على الاعتبارات الأخرى، مثل الطاقة والتكلفة.

على الرغم من أنه أرخص من HBM4 أو HBM4E، إلا أن SPHBM4 لا يزال يتطلب قوالب HBM DRAM المكدسة التي تكون أكبر ماديًا وبالتالي أكثر تكلفة من شرائح DRAM السلعية، وقالب قاعدة الواجهة، ومعالجة TSV، وتدفقات القالب الجيدة المعروفة، والتجميع المتقدم داخل العبوة. تهيمن هذه الخطوات على التكلفة والحجم بشكل سيئ مقارنة بالسلعة GDDR7، والتي تستفيد من الأحجام الهائلة للمستهلكين والألعاب، والحزم البسيطة، وتجميع PCB الناضج.

ومع ذلك، فإن استبدال العديد من شرائح GDDR7 بشريحة SPHBM4 متقدمة واحدة قد لا يقلل التكاليف؛ فقد يزيدهم.

الفن يكمن في تفاصيل التنفيذ

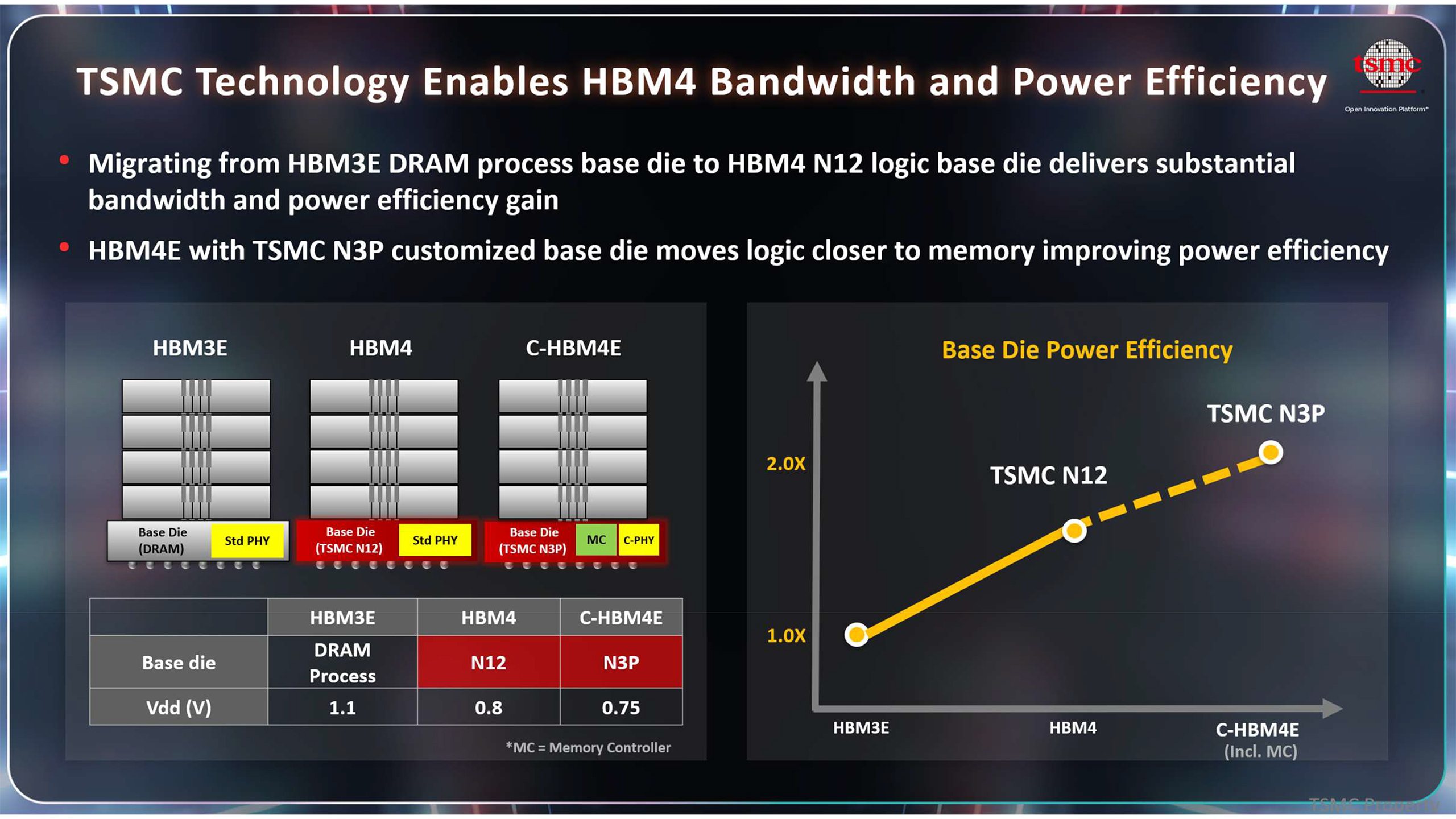

في حين أن ناقل الذاكرة 512 بت يظل واجهة معقدة، تقول JEDEC إن SPHBM4 يتيح التكامل 2.5D على الركائز العضوية التقليدية ولا يتطلب وسيطات باهظة الثمن، مما يخفض تكاليف التكامل بشكل كبير ويحتمل أن يوسع مرونة التصميم. وفي الوقت نفسه، من خلال واجهة 512 بت متوافقة مع معايير الصناعة، يمكن أن يوفر SPHBM4 تكاليف أقل (بفضل الحجم الذي تم تمكينه بواسطة التقييس) مقارنة بحلول C-HBM4E التي تعتمد على UCIe أو واجهات خاصة.

بالمقارنة مع الحلول القائمة على السيليكون، يتيح توجيه الركيزة العضوية أطوال قنوات كهربائية أطول بين SoC ومكدسات الذاكرة، مما يحتمل أن يخفف قيود التخطيط في الحزم الكبيرة ويستوعب سعة ذاكرة أكبر بالقرب من الحزمة مما هو ممكن حاليًا. ومع ذلك، من الصعب تخيل توجيه واجهة ذاكرة 3084 بت (إلى جانب البيانات وأسلاك الطاقة) باستخدام ركائز تقليدية، لكننا سنرى ذلك.

يتبع أجهزة توم على أخبار جوجل، أو أضفنا كمصدر مفضل، للحصول على آخر الأخبار والتحليلات والمراجعات في خلاصاتك.

التعليقات